#### A Cloud-Based GUI for Accelerating SoC Design

#### INTRODUCTION

Problem Statement ChipShop Introdcution

#### **FEATURES**

Web based SoC Generation FPGA Mapping and Bitstream Generation Blackbox (IP) Integration Real-time Collaboration and Version Control

#### **TECHNICAL**

Applications Tech Stack

#### CONCLUSION Q/A

# AGENDA

## PROBLEM STATEMENT

- Designing a System-on-Chip (SoC) is out of reach due to the high level of technical expertise required.

- It stifles innovation and advancement in the industry.

- Need for auser-friendly approach to SoC design.

- To make the design process easier and more efficient.

- In addition, it should democratise access to SoC design by making it broadly available to individuals without deep technical knowledge.

- This issue is already resolved by Chipyard, however using it and creating customised SoCs with it takes more technical know-how, making it only useful for a some specified users.

## CHIPSHOP

- ChipShop, a web-based GUI built on top of Chipyard.

- It enables users to configure and accelerate the SoC generation.

- Easy-to-use interface for Chipyard configuration.

- Streamlines the SoC design process and makes it accessible to a broader range of users.

- Addition of new IPs and automatic blackbox generation and integration for user-provided RTLs.

- Well-suited for large teams working on complex designs

## FPGA Mapping and Bitstream Generation

**Real-time Collaboration** and Version Control

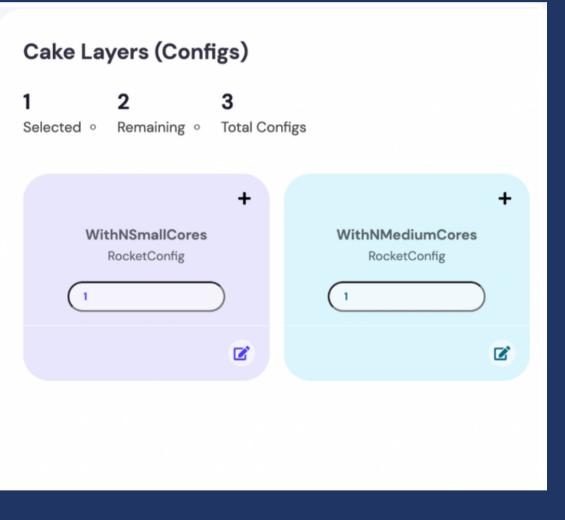

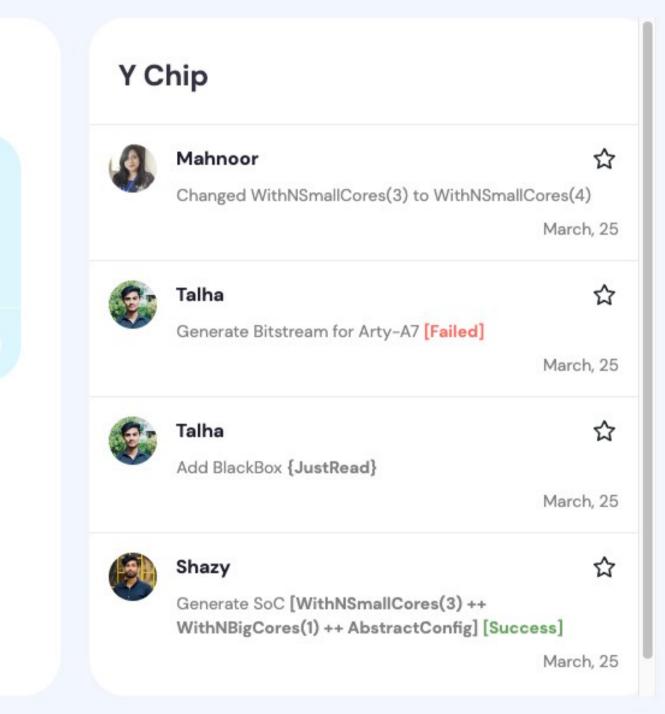

## WEB BASED SOC CONFIGURATION

System-on-Chip (SoC) Configuration is done on the basis of Chipyard Cake Pattern. Users can add, remove, and edit cake layers (configs) to create a customised SoC.

All the Configuration classes (Cake layers) can be added to create a custom System-on-Chip (SoC)

#### Cake Layers (Configs)

| 1          | 2                             | 3        |        |                                  |   |

|------------|-------------------------------|----------|--------|----------------------------------|---|

| Selected o | Remaining o                   | Total Co | onfigs |                                  |   |

|            |                               | +        |        |                                  | + |

|            | thNSmallCores<br>RocketConfig |          |        | WithNMediumCores<br>RocketConfig |   |

| 1          |                               |          | (      | 1                                |   |

|            |                               | Ø        |        |                                  | C |

|            |                               |          |        |                                  |   |

|            |                               |          |        |                                  |   |

|            |                               |          |        |                                  |   |

Editing Parameters for all Cake layers

In addition, the parameters of those Configuration classes (Cake layers) can also be edited (customised) -ChipShop

## Cake Layers (Configs)

0 0 0 Selected o

Remaining o **Total Configs**

Cake (System on Chip) :≡ 88 Generate

6 C A 6 Sur 5-07

## FPGA MAPPING AND BITSTREAM GENERATION

ChipShop also offers Bitstream Generation of the generated SoC , along with mapping its I/Os onto FPGA components.

Users can select FPGA target from the available targets to generate bitstream for it

In addition, the I/Os of the SoC like UART, SPI more custom IP I/Os can be mapped onto FPGA components

## REAL-TIME COLLABORATION AND VERSION CONTROL

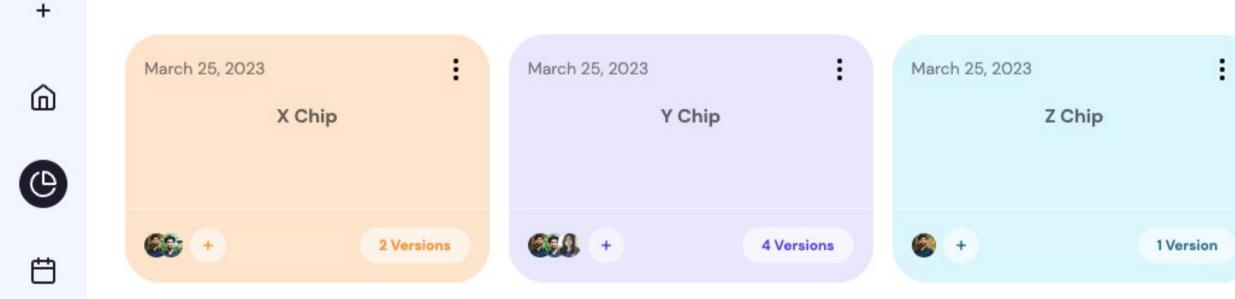

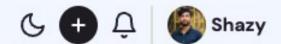

ChipShop also offers the feature of Real Time Collaboration and Version Control for each of the SoC Projects users create.

Share you SoC Project with others

Users can share their SoC Project with other Users, registered in ChipShop Workspace.

Version maintained history of changes

For every small change made by each user on a single project, after SoC Generation. Version based history is maintained.

#### - ChipShop

\$

#### Projects

## BLACKBOX (IP) INTEGRATION

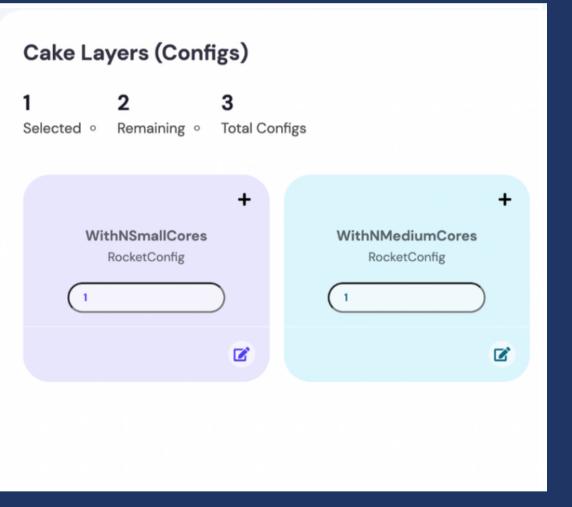

Cake Layers (Configs)

| 1 2                    | 3        |                  |

|------------------------|----------|------------------|

| Selected • Remaining • | Total Co | onfigs           |

|                        | +        | +                |

| WithNSmallCores        |          | WithNMediumCores |

| RocketConfig           |          | RocketConfig     |

| 1                      |          | 1                |

|                        | Ø        | ľ                |

|                        |          |                  |

|                        |          |                  |

|                        |          |                  |

Users can also attach their own Custom IPs with the System on Chip as an Memory Mapped Input Output (MMIO).

ChipShop features quick and easy integration of User IP into the SoC Address Space, at user's defined custom address.

#### Map the IP's I/Os to FPGA via ChipTop

The I/Os of the IP can be routed to ChipTop in order to be mapped onto FPGA.

ChipShop -

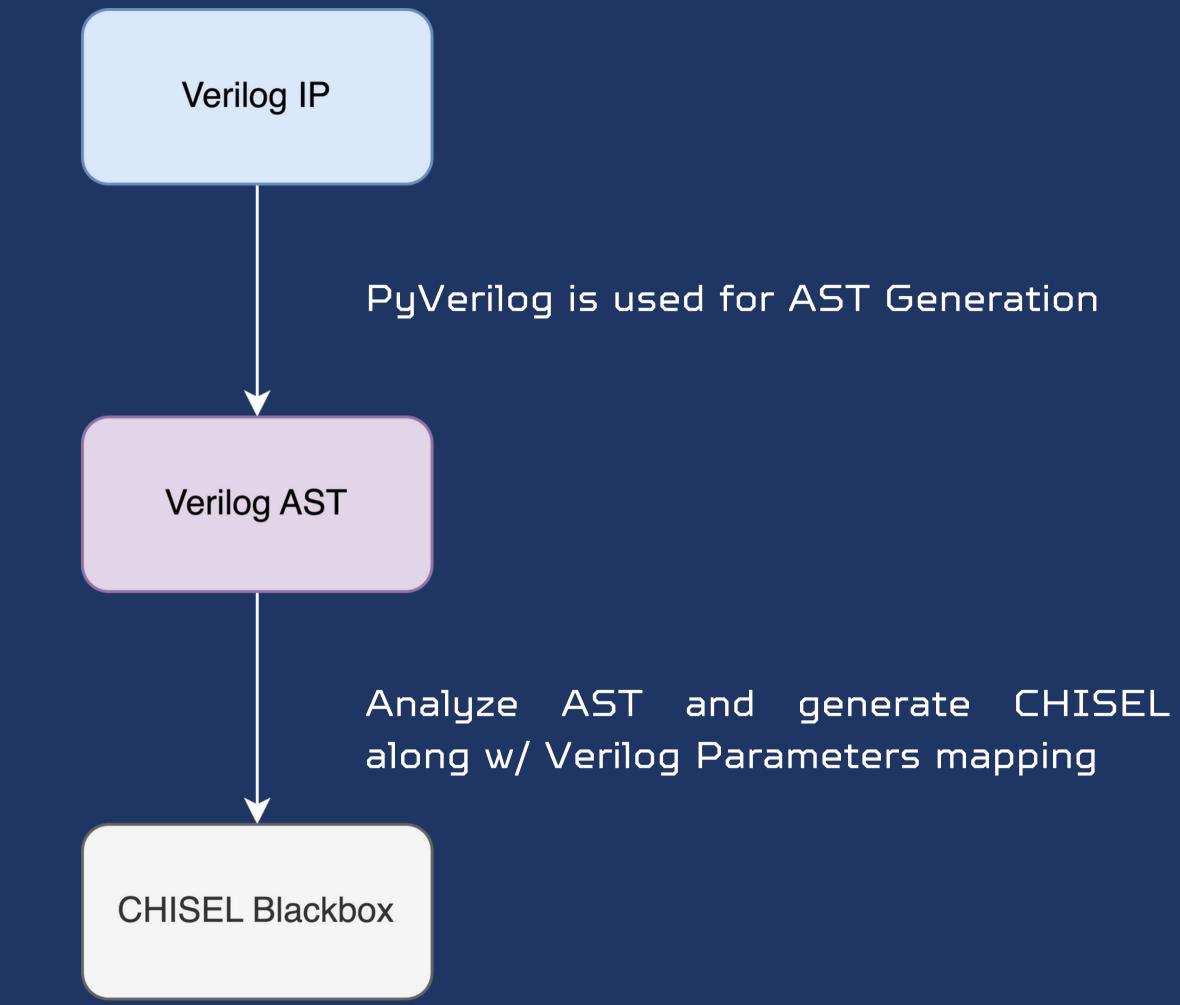

## chiV: CHISEL INTERFACING FOR VERILOG IP5

In addition to the Blackbox Integration feature, we have created a utility software for Interfacing of Verilog IPs into CHISEL HDL.

#### Technical

## APPLICATIONS

- Custom SoC design for specialized applications (IoT, automotive, aerispace).

- Educational purposes: learning tool to teach SoC design concepts to students.

- Rapid prototyping and testing of SoC designs

- Startups or small companies.

- Large organizations that want to accelerate the SoC design.

- CHISEL

- Scala

- Python

- DJANGO-REST

- REACT

- Docker

### Dr. Farhan Ahmed Karim

# Chipshop Feam

#### Conclusion

## FUTURE WORK

- To extend support for FireSim.

- Additionally, to expand Bitstream Generation support using open-source tools.

- Add more targets for FPGA Platforms.

#

## Any Questions?

sispace.tech/chipshop