# **Robust but Relaxed Probing Model**

Nicolai Müller<sup>1</sup> and Amir Moradi<sup>2</sup>

<sup>1</sup> Ruhr University Bochum, Horst Görtz Institute for IT Security, Bochum, Germany firstname.lastname@rub.de

<sup>2</sup> Technische Universität Darmstadt, Darmstadt, Germany firstname.lastname@tu-darmstadt.de

**Abstract.** Masking has become a widely applied and heavily researched method to protect cryptographic implementations against Side-Channel Analysis (SCA) attacks. The success of masking is primarily attributed to its strong theoretical foundation enabling it to formally prove security by modeling physical properties through socalled probing models. Specifically, the robust *d*-probing model enables us to prove the security for arbitrarily masked hardware circuits, manually or with the assistance of automated tools, even when considering the imperfect nature of physical hardware, including the occurrence of physical defaults such as glitches. However, the generic strategy employed by the robust *d*-probing model comes with a downside: It tends to over-conservatively model the information leakage caused by glitches meaning that the robust *d*-probing model considers glitches that can never occur in practice. This implies that in theory, an adversary could gain more information than she would obtain in practice. From a designer's perspective, this entails that (1) securely designed hardware circuits may need to be withdrawn due to potential insecurity under the robust d-probing model and (2) designs that satisfy the security requirements of the robust *d*-probing model may incur unnecessary overhead, such as increased circuit size or latency.

In this work, we refine the formal treatment of glitches within the robust d-probing model to address glitches more accurately within a formal adversary model. Unlike the robust d-probing model, our approach considers glitches based on the operations performed and the data processed, ensuring that only manifesting glitches are accounted for. As a result, we introduce the Robust but Relaxed (RR) d-probing model, a formal adversary model maintaining the same level of security as the robust d-probing model but without the overly conservative treatment of glitches. Leveraging our new model, we prove the security of LUT-based Masked Dual-Rail with Pre-charge Logic (LMDPL) gadgets, a class of physically secure gadgets reported as insecure based on the robust d-probing model. We provide manual proofs and automated security evaluations employing an updated version of PROLEAD capable of verifying the security of masked circuits under our new model.

Keywords: Side-Channel Analysis · Masking · Hardware · Robust Probing Model

# 1 Introduction

More than two decades after Kocher's seminal discovery [Koc96], the task of securing cryptographic hardware implementations against the pervasive threat of SCA attacks remains a formidable challenge. In this context, the masking countermeasure [CJRR99], based on encoding secret variables through multiple shares [Sha79], emerges as the most widely adopted and thoroughly comprehended technique, especially concerning its formal security assurances [ISW03, PR13, DDF14, DFS15]. In concrete terms, if the leakages of the shares achieve a sufficiently high noise level and are independent of each other,

the number of required measurements (i.e. the complexity) of SCA attacks increases exponentially with the number of shares [CJRR99]. Masking aims to randomize every sensitive variable X by splitting it into d+1 shares, denoted as  $X^0, \ldots, X^d$ , in a manner such that their sum<sup>1</sup> equals X. For instance, in the prevalent Boolean masking, where  $X \in \mathbb{F}_2$ , it holds that  $X = X^0 \oplus \ldots \oplus X^d$ , with all shares  $X^i \in \mathbb{F}_2$   $(0 \le i \le d)$  following a uniform distribution. To assess the practical fulfillment of the aforementioned requirements concerning independence and noise, formal security models abstract the physical security of masking. The basic *d*-probing model introduced by Ishai et al. [ISW03] enables to validate if an adversary needs to observe at least d intermediates, i.e. stable signals carried by physical wires, in a masked hardware circuit to make any inference about a secret variable. This is modeled by placing up to d so-called probes, each recording one stable signal. In essence, evaluation under the *d*-probing model ensures the preservation of the independence property, while achieving a sufficient noise level is imperative for security even in the most realistic noisy leakage model [PR13]. However, despite the adequacy of the noise level, multiple case-studies have demonstrated that a scheme deemed d-probing secure may still fall short of providing the expected level of security against SCA attacks in practical scenarios [MPO05, MPO05]. This unexpected leakage arises from the asynchronous arrival of input signals at a combinational gate. In such scenarios, the gate may produce a transient and unintended change in its output signal before stabilizing, commonly known as a glitch [Rab96]. Therefore, if the inputs of a combinational gate toggle, it does not merely result in a single toggle from one stable output value to another, as presumed by the *d*-probing model. Instead, it may trigger a sequence of toggles caused by glitches before the output stabilizes. This pattern, which can be observed at the gate's output, subsequently propagates as an input signal to the following combinational logic while leaking not only the stable output of the gate but also additional information about the input signals, an aspect not accounted for by the *d*-probing model. Therefore, the robust d-probing model, as introduced in [FGP<sup>+</sup>18], extends the foundational d-probing model to encompass the additional information leaked due to glitches. In this model, glitch-extended probes are introduced to capture not only stable signals but also potential signals revealed by glitches. However, due to the computational hardness of checking for specific glitches, the model assumes a generic worst-case scenario. Thus, a glitch-extended probe on a wire can record all stable signals from the combinational logic contributing to the probed wire. This assumption enables the assessment of security under the robust *d*-probing model without requiring knowledge of the specific placement and routing of the final design. Consequently, security proofs under this model hold for arbitrary circuits, independent of their particular placement and routing. The simplicity and broad applicability of the robust *d*-probing model have led to its widespread adoption for evaluating masked hardware. It is integrated into various tools such as [BGI<sup>+</sup>18, KSM20, MM22, BMRT22], facilitating automatic assessment of security for masked implementations. However, the model adopts a worst-case scenario approach, accounting for all potential glitches, despite only a subset of these glitches manifesting in practical scenarios. This tendency towards over-conservatism implies that a masked circuit, potentially optimized for efficiency, may remain secure in real-world applications even if deemed insecure under the robust *d*-probing model. This disparity between robust probing security and real-world security becomes particularly evident when considering glitch-free circuits. For instance, in [MLM23], it was demonstrated that such circuits leak more information than assumed by the *d*-probing model. However, considering glitches in such circuits is irrelevant as no glitches can occur. Specifically, the study revealed that LMDPL is not secure under the robust probing model, while also confirming its security and noting the absence of an accurate model to evaluate such circuit types.

$<sup>^{1}\</sup>mathrm{By}$  "sum" we refer to the result of the addition of all shares in the underlying finite field.

### 1.1 Our Contributions

In this work, we propose a refinement of the robust d-probing model, aiming to reduce its over-conservatism while maintaining an equivalent level of security assurance. Our contributions are as follows:

- We introduce the RR *d*-probing model, a formal adversary model that provides a more precise treatment of glitches compared to the robust *d*-probing model, while ensuring an equivalent level of security<sup>2</sup>. Therefore, we propose a probe-extension procedure that specifically accounts for glitches based on the performed operations and processed data. Consequently, our model exclusively address glitches that manifest within a hardware circuit in a formal manner.

- We close the lack of accurate and formal proofs when assessing the security of glitch-free circuits as pointed out in [MLM23]. In particular, within our model, we can formally prove the security of LMDPL [LMW14] as well as the insecurity of Self-Synchronized Masking (SESYM) [NGPM22].

- To automate the security evaluation within our refined model, we extended the functionality of the existing PROLEAD tool [MM22] with the evaluation of a provided gate-level netlist under our model. Our extension is available as an open-source contribution via GitHub<sup>3</sup>.

# 2 Background

### 2.1 Notations

We denote all random variables, like  $X \in \mathbb{F}_2$ , by capital letters and sets, like  $\mathbf{X}$ , by bold capital letters. We use subscripts to denote specific elements within a set, e.g., we denote the elements of a set  $\mathbf{X}$  with  $|\mathbf{X}| = n$  as  $X_0, \ldots X_{n-1}$ . When denoting functions, e.g.  $\mathsf{F} : \mathbb{F}_2^n \to \mathbb{F}_2^m$ , we use sans-serif fonts. Further, we use superscripts to denote individual shares of a shared variable. For example, a sensitive variable X is shared as  $X^0 \oplus \ldots \oplus X^{d-1}$ . Furthermore, the set of shares associated with a set of n secret variables  $\mathbf{X}$  is denoted as  $Sh(\mathbf{X}) = [X_0^0, \ldots X_0^{d-1}, \ldots, X_{n-1}^0, \ldots X_{n-1}^{d-1}].$

## 2.2 Circuit Model

We model any stateful and deterministic circuit as a Directed Acyclic Graph (DAG) G = (V, E) whose vertices in set V are atomic components (gates), embodying the underlying logic, and edges in set E are interconnections (wires), transmitting elements from  $\mathbb{F}_2$  [ISW03]. In this work, we specify different types of gates as follows:

- Combinational gates of fan-in at most 2 and fan-out 1 compute a logic function on its inputs without any dependence on the prior states of inputs. Without loss of generality, we restrict the logic functions processed by combinational gates to {NOT, AND, NAND, OR, NOR, XOR, XNOR}.

- Sequential gates of fan-in 1 and fan-out 1 compute a logic function on its current inputs but also on previous inputs. All sequential gates are clock-synchronized.

- Input gates of fan-in 0 and fan-in 1 write elements in  $\mathbb{F}_2$  on a wire.

$<sup>^2 \</sup>rm With$  "equivalent level of security" we mean that both models capture all leakages caused by glitches that can physically manifest.

<sup>&</sup>lt;sup>3</sup>https://github.com/ChairImpSec/PROLEAD

• Output gates of fan-in 1 and fan-in 0 read elements in  $\mathbb{F}_2$  from a wire.

However, this circuit model does not apply for iterative circuits, i.e. circuits with the ability to evaluate the same gate within multiple clock cycles, and was, therefore, extended by the structural circuit model given in [CS21]. This model defines a structural circuit as a directed graph, without any combinational loop, whose vertices are structural gates and edges are structural wires, carrying different elements across various time instances (clock cycles). Hence, a structural wire W is represented as a pair (E, t), comprising a wire E and a specific time instance t. According to Definition 4 in [CS21], the execution of a structural circuit for a set of clock cycles models the state of the circuit for the given set of clock cycles as well as the latency introduced by sequential gates.

## 2.3 Circuit Compiler

A circuit compiler encompasses three different algorithms (CC, ENC, DEC), defined as follows [AIS18]:

- The deterministic circuit compilation algorithm CC expects a (structural) circuit C as input and returns a randomized (masked) (structural) circuit  $\tilde{C}$ .

- The probabilistic encode algorithm ENC expects the set of unshared inputs **X** of C and returns the *d*-shared input  $\tilde{\mathbf{X}} = Sh(\mathbf{X})$  of  $\tilde{\mathsf{C}}$ .

- The deterministic decode algorithm DEC expects the shared output  $\ddot{\mathbf{Y}} = Sh(\mathbf{Y})$  of  $\ddot{C}$  and returns the set of unshared outputs  $\mathbf{Y}$  of C.

We note that the resulting  $\tilde{C}$  may include additional randomness gates with a fan-in 0 and fan-out 1, which produce a uniformly distributed random value in  $\mathbb{F}_2$ . When viewed as a structural circuit, all randomness gates in  $\tilde{C}$  generate a fresh uniformly distributed random value per clock cycle.

## 2.4 Adversary Model

In this work, we focus on passive adversaries possessing the capability to observe a masked circuit  $\tilde{C}$ . This implies that the adversary lacks direct access to secret data **X** or **Y**, even if the underlying circuit compiler is public. Initially, we assume that  $\tilde{C}$  is modeled as a DAG as introduced in Subsection 2.2 while we introduce all relevant definitions for structural circuits when necessary.

#### 2.4.1 *d*-probing Model

The basic *d*-probing model [ISW03] defines the *d*-probing adversary with the ability to observe up to *d* intermediate elements processed by  $\tilde{C}$ . In the following, we denote the set of observations made by an adversary as **Q**. The observation is abstracted by permitting an adversary to place up to *d* standard probes, as formalized in Definition 1, on arbitrary wires of  $\tilde{C}$ .

**Definition 1** (Standard Probe). Let  $\tilde{C}$  be a masked circuit with G = (V, E). A standard probe  $P_E \in \mathbb{F}_2$  on wire  $E \in E$  symbolically represents the element in  $\mathbb{F}_2$  carried by wire E.

Intuitively,  $\tilde{\mathbf{C}}$  achieves *d*-probing security if no *d*-probing adversary can extract secret (unshared) data by observing the joint distribution of at most *d* intermediate elements. Formally, we define *d*-probing security based on the concept of statistical independence. Let  $\mathbf{A}$  and  $\mathbf{B}$  be two sets of discrete random variables. Then,  $\mathbf{A}$  is statistically independent of  $\mathbf{B}$  iff it holds that  $Pr[\mathbf{A}|\mathbf{B}] = Pr[\mathbf{A}]$ .

**Definition 2** (*d*-Probing Security). A masked circuit  $\tilde{C}$  with secret input **X** is *d*-probing secure iff for any set of standard probes **P** with  $|\mathbf{P}| \leq d$ , the joint distribution over all observations **Q** made by the standard probes in **P** is statistically independent of **X**.

#### 2.4.2 Robust *d*-Probing Model

The robust *d*-probing model [FGP<sup>+</sup>18] extends the *d*-probing model by incorporating the impact of a limited set of physical defaults, namely combinational recombinations (glitches) [MPG05], memory recombinations (transitions) [CGP<sup>+</sup>12], and routing recombinations (couplings) [CBG<sup>+</sup>17], on the formal security of  $\tilde{C}$ . The robust *d*-probing model introduces a novel class of probes, referred to as extended probes, for each of the three discussed physical defaults. These extended probes not only observe the elements carried by the wires they are placed on but also observe elements carried by other wires. Hence, every extended probe symbolically represents a set of standard probes.

**Glitch-Extended Probe.** A Glitch-extended probe models the fact that when measuring the signal driven by a physical wire we do not just see the stable signal immediately. Instead, we observe a sequence of transient toggles before the signal stabilizes. Since glitches are data-dependent, observing such a sequence can yield information about multiple signals connected to the observed wire through combinational logic. In the robust-probing model, it is assumed conservatively that glitches might enable an adversary to access all signals that contribute to the computation of the observed wire via combinational logic. Consequently, a glitch-extended probe on wire E, denoted as  $P_E^{\text{ext}}$ , is converted into a set of standard probes placed on all primary inputs and register outputs that contribute to E. As shown in [KM22], we formalize the glitch-extension procedure with function name glitch\_extend in Algorithm 1.

| Algorithm 1 Glitch Extension (glitch_extend)                                                                                             |                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Input: $P_E^{\text{ext}}$                                                                                                                | $\triangleright$ Glitch-extended probe on wire $E$ |

| Output: P                                                                                                                                | $\triangleright$ The set of standard probes        |

| 1: if $P_E^{\text{ext}}$ is placed on an output of a combination                                                                         | al gate <b>then</b>                                |

| 2: $\mathbf{\tilde{P}} \leftarrow \bigcup_{i=0}^{n} \texttt{glitch\_extend}(P_i^{\text{ext}}) \triangleright P_i^{\text{ext}} \text{ w}$ | ith $0 \le i < n$ denotes glitch-extended          |

| probes on all inputs of the combinational gate                                                                                           |                                                    |

| 3: else                                                                                                                                  |                                                    |

| 4: <b>if</b> $P_E^{\text{ext}}$ is placed on an output of a sequential                                                                   | al gate or a primary input <b>then</b>             |

| 5: $\mathbf{\overline{P}} \leftarrow \{P_E\}$                                                                                            |                                                    |

| 6: end if                                                                                                                                |                                                    |

| 7: end if                                                                                                                                |                                                    |

**Transition-Extended Probe.** A transition-extended probe models the dependence of the consumed energy on both the preceding and subsequent elements when overwriting a wire. Consequently, a transition-extended probe placed on a structural wire W = (E, t) observes a pair of elements carried by wire E during clock cycles t - 1 (the preceding element) and t (the subsequent element)[CS21]. Similarly, the transition-extension procedure transforms a transition-extended probe on wire W = (E, t) into two standard probes. These standard probes separately represent the elements carried by e during clock cycles t and t - 1. For simplicity, we omit the specific value of t if it is not relevant and refer to the result of a transition-extension procedure as  $(P_{E'}, P_E)$ . Here,  $P_{E'}$  denotes a standard probe on wire E observing the preceding element, while  $P_E$  observes the subsequent element. While glitches and transitions are formally treated as distinct phenomena, it's noteworthy that glitch-extended probing, in isolation from transitions, oversimplifies the situation, given

that glitches are a direct consequence of transitions. Consequently, we advocate for a holistic approach that incorporates both glitches and transitions when employing formal adversary models. To consider glitches and transition simultaneously, both extended probes can be merged resulting in the extension procedure robust\_extend outlined in Algorithm 2. Now, a so-called robust probe on wire E, denoted as  $P_E^{\text{robust}}$ , is converted into a set of standard probes recording two consecutive states of all primary inputs and register outputs that contribute to E. First, the glitch-extension procedure is performed as shown in Algorithm 1 until the probe cannot be further extended based on glitches. Afterwards, in the result of the glitch extension becomes transition-extended (cf. Line 5) by storing standard probes on the respective wire's preceding and subsequent element.

Algorithm 2 Robust (Glitch and Transition) Extension (robust extend)

| Input: $P_E^{\text{robust}}$                                                                        | $\triangleright$ Robust probe on wire $E$                              |

|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Output: P                                                                                           | $\triangleright$ The set of standard probes                            |

| 1: if $P_E^{\text{robust}}$ is placed on an output of a combined                                    | inational gate <b>then</b>                                             |

| 2: $\mathbf{\tilde{P}} \leftarrow \bigcup_{i=0}^{n} \texttt{robust\_extend}(P_{i}^{\text{robust}})$ | $\triangleright P_i^{\text{robust}}$ with $0 \le i < n$ denotes robust |

| probes on all inputs of the combinational ga                                                        |                                                                        |

| 3: else                                                                                             |                                                                        |

| 4: <b>if</b> $P_E^{\text{robust}}$ is placed on an output of a sec                                  | quential gate or a primary input <b>then</b>                           |

| 5: $\overline{\mathbf{P}} \leftarrow \{P_{E'}\} \cup \{P_E\}$                                       | $\triangleright$ Do the transition extension                           |

| 6: end if                                                                                           |                                                                        |

| 7: end if                                                                                           |                                                                        |

We remark that we do not consider couplings in this work as the circuit models discussed in Subsection 2.2 do not incorporate any information regarding placement and routing. Consequently, in the variant of the robust *d*-probing model that considers glitches and transitions but excludes couplings, which we refer to as the robust probing model for the rest of this work, an adversary, denoted as a robust *d*-probing adversary, can place a maximum of *d* robust probes on arbitrary wires within  $\tilde{C}$ .

**Definition 3** (Robust *d*-Probing Security). A masked circuit  $\tilde{C}$  with secret input **X** is robust *d*-probing secure iff for any set of robust probes **P**, with  $|\mathbf{P}| \leq d$ , the joint distribution over all observations **Q** made by the robust probes is statistically independent of **X**.

### 2.4.3 Composability

However, finding a compiler that transforms a circuit C into an efficient and robust *d*-probing secure masked circuit  $\tilde{C}$  as well as verifying the *d*-probing security of  $\tilde{C}$  poses a challenge, especially if C is complex and *d* is high. Therefore, composable gadgets were introduced in [CGLS21] to establish a standard compiler. This compiler replaces every gate of C with its corresponding gadget. Each gadget itself is a robust *d*-probing secure circuit, implementing the functionality of a basic logic gate. Furthermore, these gadgets achieve composability under a certain composability notion implying robust *d*-probing security, even when multiple gadgets are arbitrarily composed to form a larger circuit. Before introducing the composability notion employed in this work, we first introduce the concept of probe simulatability [CS20]. This concept enables us to formally reason about the dependencies between (robust) probes and input shares to  $\tilde{C}$ .

**Definition 4** (Perfect Probe Simulation). Let  $\mathbf{P} \in \mathbb{F}_2^t$  be a set of robust probes on a masked circuit  $\tilde{C}$  and  $\mathbf{S} \subset \tilde{\mathbf{X}}$  be a set of input shares. Further, let  $\mathsf{SIM}(\mathbf{S}) : \mathbb{F}_2^{|\mathbf{S}|} \to \mathbb{F}_2^t$  be a probabilistic polynomial time simulator. **P** is perfectly simulatable by a set **S** iff there exist a simulator SIM, such that for any values of the inputs to  $\tilde{C}$ , the joint probability distribution over **P** and  $\mathsf{SIM}(\mathbf{S})$  are equal.

$\mathbf{6}$

Now, let  $P \in \mathbb{F}_2$  be a probe on a masked circuit (gadget)  $\tilde{C}$ . We say that P propagates into an input of  $\tilde{C}$  if the input is required to perfectly simulate P. Consequently, the concept of probe propagation defines the information leaked by a probe and how this leakage is propagated throughout the circuit [CS20]. To ensure the composability of a gadget, the Probe-Isolating Non-Interference (PINI) composability notion [CS20] constrains the probe propagation of all probes on outputs to its own share domain. Similarly, it limits the probe propagation of probes on internal wires of the gadget to a single but arbitrary share domain. The concept of share domains is defined in [GMK16], while Definition 5 formally introduces the PINI notion.

**Definition 5** (Robust *d*-Probe-Isolating Non-Interference (PINI)). Let  $\tilde{C}$  be a masked circuit with secret input **X**. Further, let  $\mathbf{P}_{I}$  be a set of robust probes on internal wires of  $\tilde{C}$  with  $|\mathbf{P}_{I}| = t_{1}$  and  $\mathbf{I}_{O}$  be the set of indices assigned to the robust probes on output wires in the set  $\mathbf{P}_{O}$  with  $|\mathbf{I}_{O}| = t_{2}$ .  $\tilde{C}$  is robust *d*-PINI iff for every  $\mathbf{P} = \mathbf{P}_{I} \cup \mathbf{P}_{O}$  with  $t_{1} + t_{2} \leq d$ , there exists a set of indices  $\mathbf{I}_{I}$  with  $|\mathbf{I}_{I}| \leq t_{1}$  such that  $\mathbf{P}$  is perfectly simulatable from  $\mathbf{S} = \tilde{\mathbf{X}}^{\mathbf{I}_{I} \cup \mathbf{I}_{O}}$ .

# **3** Dynamic Power Consumption of CMOS Circuits

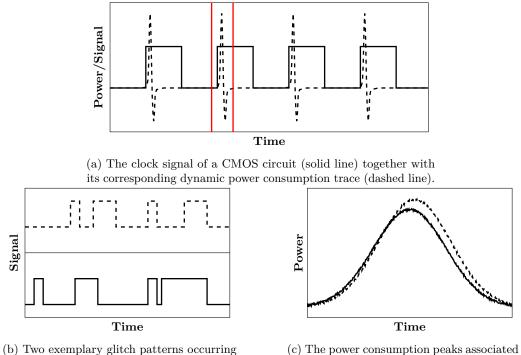

Following the formal introduction to how glitches are modeled within the robust *d*-probing model, it becomes crucial to elaborate on why this model accurately reflects the physical reality regarding glitches. To illustrate this, we examine the dynamic power consumption of a Complementary Metal-Oxide-Semiconductor (CMOS) circuit, as schematically depicted in Figure 1a. In CMOS circuits, synchronization is achieved through a clock signal, with all sequential gates evaluating with every (rising or/and falling) edge of the clock signal. Consequently, the dashed signal in Figure 1a exhibits distinct power peaks corresponding to each rising edge of the clock, with each peak dependent on the power consumption of the combinational logic. Notably, every change at a CMOS gate contributes to the amount of dynamic power consumption. Hence, glitches have a significant impact on this amount. To further elaborate this, we consider two exemplary patterns of glitches as visualized in Figure 1b which can be the result of two distinct transitions at the input of a combinational circuit, i.e., at the registers which provide such inputs.

Clearly, distinguishing between these patterns is straightforward when the entire patterns are observable. Additionally, it can be assumed that each transition at the input of the combinational logic yields a unique glitch "fingerprint", manifested as a pattern of glitches in the outputs of the combinational logic. Consequently, observing a pattern of glitches may reveal all inputs of the combinational logic. One might argue that exploiting such a pattern necessitates an SCA attack that combines a sequence of leakage samples, namely a multivariate attack [GBPV10], which can be challenging to mount in practice. However, it is important to note that, in the context of power consumption, the measured power is filtered by a low-pass filter [MOP07]. The limited bandwidth of this filter implies that obtaining distinct power signals for logic cells that switch within a few nanoseconds, such as those related to glitches, is not feasible. We sketched the power consumption peaks associated with the shown glitch patterns in Figure 1c. Notably, these peaks encompass the sum of all consumed power within a single clock cycle, i.e. all glitches occurring within one clock cycle, their shape, and their duration contribute to the peak. Consequently, a single leakage sample in a measured power trace is influenced by the switching activities of cells within a certain time interval shorter than a full clock cycle [MOP07]. Therefore, it is possible to find at least a single leakage sample to differentiate these power consumption peaks. Hence, the whole information leaked by a pattern of glitches becomes observable in a single leakage sample effectively making univariate first-order attacks applicable [MPO05]. The robust *d*-probing model operates under the premise that each input state of the combinational logic results in a distinctive

within one clock cycle.

(c) The power consumption peaks associated with these glitch patterns.

Figure 1: The dynamic power consumption of a CMOS circuit.

power consumption peak and that these peaks can be distinguished by a single leakage sample. In particular, it acknowledges that observing a single leakage sample may provide information on all inputs of the combinational logic. It achieves this by defining robust probes that grant access to additional standard probes across all these inputs.

# 4 Technique

Let  $\tilde{C}$  be a masked circuit with secret input **X** and  $P_E^{\text{robust}}$  be a robust probe on an arbitrary wire E of  $\tilde{C}$ . According to Algorithm 2, if E is the output of a combinational gate  $P_E^{\text{robust}}$  gets substituted by robust probes on all input wires of the combinational gate. However, if E is a primary input or the output of a sequential gate,  $P_E^{\text{robust}}$  is not further extended but substituted by two standard probes  $P_{E'}$  and  $P_E$  on two consecutive clock cycles.

Line 1 of Algorithm 2 highlights a significant disparity between the treatment of glitches in the robust probing model and their manifestation in physical reality. The robust *d*-probing model relies on the conservative assumption that a probe on the output of a combinational gate extends to all inputs of such a gate independent of the operation performed by the combinational gate and independent of the processed data. However, the physical manifestation of glitches is significantly influenced by both the operation executed by the gate and the data processed by it. We illustrate this in Example 1. In particular, we show one scenario where the operation performed by the gate together with the processed data leads to a stop of the glitch-propagation.

**Example 1.** Consider an AND-gate with two inputs X and Y and output Z. If X (resp. Y) is constantly set to zero, a glitch on Y (resp. X) cannot lead to a glitch on Z. This means that the glitch-propagation stops at this gate without the need for a sequential gate.

Moreover, if X (resp. Y) is constantly set to zero, an adversary who observes Z being constantly zero cannot learn Y (resp. X) while a robust d-probing adversary gets access to two robust probes  $P_X^{\text{robust}}$  and  $P_Y^{\text{robust}}$  by placing one robust probe  $P_Z^{\text{robust}}$ .

To investigate the data- and operation-dependent propagation of glitches in more detail, we examine all possible transitions at the inputs of AND- and OR-gates with inputs X and Y and output Z. We assume that both gates are in a stable state, i.e. no glitches on X and Y, before switching to another state. In Table 1, we show all possible transitions, denoted as a set **S**, visualized by its corresponding signal waveforms. While our discussion focuses solely on specific AND- and OR-gates, we provide similar tables for other combinational gates with fan-in two in the Appendix.

|              |   | Table 1 | Signal wave |

|--------------|---|---------|-------------|

| $\mathbf{S}$ | X | Y       | Z           |

| $S_0$        |   |         |             |

| $S_1$        |   |         |             |

| $S_2$        |   |         |             |

| $S_3$        |   |         |             |

| $S_4$        |   |         |             |

| $S_5$        |   |         |             |

| $S_6$        |   |         |             |

| $S_7$        |   |         |             |

| $S_8$        |   |         |             |

| $S_9$        |   |         |             |

| $S_{10}$     |   |         |             |

| $S_{11}$     |   |         |             |

| $S_{12}$     |   |         |             |

| $S_{13}$     |   |         |             |

| $S_{14}$     |   |         |             |

| $S_{15}$     |   |         |             |

Table 1: Signal waveforms of AND- and OR-gates.

S X

| 5        | $\Lambda$ | 1 | 2 |

|----------|-----------|---|---|

| $S_0$    |           |   |   |

| $S_1$    |           |   |   |

| $S_2$    |           |   |   |

| $S_3$    |           |   |   |

| $S_4$    | <u> </u>  |   |   |

| $S_5$    | <u> </u>  |   |   |

| $S_6$    |           |   |   |

| $S_7$    |           |   |   |

| $S_8$    |           |   |   |

| $S_9$    |           |   |   |

| $S_{10}$ |           |   |   |

| $S_{11}$ |           |   |   |

| $S_{12}$ |           |   |   |

| $S_{13}$ |           |   |   |

| $S_{14}$ |           |   |   |

| $S_{15}$ |           |   |   |

(a) Signal waveforms of an AND-gate.

(b) Signal waveforms of an OR-gate.

## 4.1 Data-Dependent Probe-Extension of an AND-gate

Initially, we investigate Table 1a and discuss the information gained by observing the waveform associated with  ${\cal Z}$

Case 1. For  $S_0$ - $S_4$ ,  $S_8$ , and  $S_{12} X$  or Y remains at a constant value of 0. These cases are similar to Example 1 and lead to a signal waveform for Z that is constantly 0. In particular, if X (resp. Y) is constantly 0 then Z is constantly 0 independent of any toggle on Y (resp. X). Hence, these observations hold true independent of any placement and routing considerations.

Case 2. For  $S_{15}$  X and Y remain at a constant value of 1. Hence, due to the underlying logic of the AND-gate,  $S_{15}$  is the only case where Z is constantly 1. Again, this holds true independent of any placement and routing considerations.

Case 3. For  $S_5$ ,  $S_7$ ,  $S_{10} - S_{11}$ , and  $S_{13} - S_{14}$  either X and Y both toggle from the same stable state to another state state (see  $S_5$  and  $S_{10}$ ) or only X (resp. Y) toggles while Y (resp. X) remains at a constant value of 1. Consequently, the waveform of Z shows the same toggle as the waveform of at least one of the inputs. As already indicated in [MLM23] the exact time of toggle on X (resp. Y) and Z depends on the delays of the

Z

wires and the AND-gate itself. This means that the observation of a single toggle on Z is not influenced by placement and routing while the exact time of toggle depends on the particular routing of the wires.

Case 4. For  $S_6$  and  $S_9 X$  and Y both toggle inversely, potentially resulting in a glitch on Z. Specifically, in  $S_6$ , a glitch arises only if X toggles prior to Y, whereas in  $S_9$ , a glitch arises only if Y toggles before X. However, if these conditions are not satisfied, no toggles occur on Z. Consequently, the presence and timing of glitches are profoundly affected by placement and routing considerations.

We reiterate that, concerning a single AND-gate, the robust *d*-probing model assumes that a robust probe  $P_Z^{\text{robust}}$  is replaced by four standard probes  $P_{X'}$ ,  $P_X$ ,  $P_{Y'}$ , and  $P_Y$ , indicating that an adversary can learn two consecutive and stable states of all inputs just by observing Z. This conservative assumption is justified by the scenarios pointed out in *Case 4*. If an adversary observes a glitch at Z, it becomes evident that we are either in scenario  $S_6$  or  $S_9$ . Furthermore, the adversary can distinctly differentiate between  $S_6$  and  $S_9$  based on the specific characteristics of the glitch, such as its timing and duration. We note that Table 1 simplifies the visualization by disregarding any potential propagation delays. In reality, however, glitches observed in scenarios like  $S_6$  and  $S_9$ may exhibit variations. Likewise, an adversary may be able to distinguish between the scenarios highlighted in *Case 3* by analyzing the precise timing of the toggles observed at Z, whereas the scenario outlined in *Case 1* remains inherently unique. This alignment of our observations underscores the validity of the robust *d*-probing model.

However, the assumption made by the robust *d*-probing model is too conservative regarding the scenarios associated with *Case* 1. In these scenarios, an adversary cannot observe any toggle on *Z*. Specifically, no timing-related information is transmitted from *X* or *Y* to *Z*, rendering it impossible to differentiate between the scenarios outlined in *Case* 1. Therefore, an adversary observing *Z* can only learn two consecutive states of *Z*, without being able to extract any additional information, about *X* and *Y*.

Based on the aforementioned observations, we propose modifying the probe-extension methodology based on the processed data and the functionality of the AND-gate. Specifically, we suggest stopping the probe-extension for all scenarios outlined in *Case* 1, while retaining the same probe-extension approach as the robust *d*-probing model for all other cases. Therefore, we define a so-called probe-extension function  $\mathsf{F}_Z^{\mathsf{AND}} : \mathbb{F}_2^4 \to \mathbb{F}_2$  for the output *Z* of an AND-gate over its consecutive input states  $X', X, Y', Y \in \mathbb{F}_2$  as given in Equation 1.

$$\mathsf{F}_{Z}^{\mathsf{AND}}(X', X, Y', Y) = (X' \lor X) \land (Y' \lor Y) \tag{1}$$

Further, we denote a variable indicating whether a robust probe on Z should be extended or not as  $F_Z \in \mathbb{F}_2$  with  $F_Z = \mathsf{F}_Z^{\mathsf{AND}}(X', X, Y', Y)$ . Equation 1 does only return 0 if one of the inputs stays at constant 0, i.e. X' = 0 and X = 0 or Y' = 0 and Y = 0, otherwise Equation 1 returns 1. Hence, if a robust probe  $P_Z^{\mathsf{robust}}$  is placed on Z we propose to place robust probes  $P_X^{\mathsf{robust}}$  and  $P_Y^{\mathsf{robust}}$  on both inputs X and Y if  $F_Z = 1$ . Otherwise, if  $F_Z = 0$ , we propose to stop the probe-extension and place two standard probes  $P_{Z'}$  and  $P_Z$  recording two consecutive states of Z.

### 4.2 Data-Dependent Glitch-Propagation of an AND-Gate

So far, we disregarded the possibility of glitches on X and Y in Table 1a meaning that we assume that the inputs of AND-gates are always free of glitches. While this assumption holds true for stable inputs, such as primary inputs or register outputs which are directly forwarded to an AND-gate, we acknowledge that glitches can occur within a combinational circuit and propagate to other combinational gates. For example, an AND-gate can receive the glitchy output of another AND-gate as input. Thus, we must adjust  $F_Z^{AND}$  to account for glitches on X and Y. Therefore, we define a so-called glitch-propagation

function  $\mathsf{G}_Z^{\mathsf{AND}} : \mathbb{F}_2^6 \to \mathbb{F}_2$  for the output Z of an AND-gate over its consecutive input states  $X', X, Y', Y \in \mathbb{F}_2$  and the information whether X or Y are already glitchy. We denote the variable indicating whether a wire X is glitchy or not as  $G_X \in \mathbb{F}_2$  and assume  $G_X = 0$  if X is a primary input or the output of a sequential gate. Otherwise, it holds that  $G_X = \mathsf{G}_X^{\mathsf{AND}}$ , i.e. the presence of glitches on X must be computed based on the inputs of the gate that calculates X. Below, we give  $\mathsf{G}_Z^{\mathsf{AND}}$  as well as a revised version of  $\mathsf{F}_Z^{\mathsf{AND}} : \mathbb{F}_2^6 \to \mathbb{F}_2$  accounting for glitches on X and Y.

$$\begin{aligned} \mathsf{F}_{Z}^{\mathsf{AND}}(X', X, G_X, Y', Y, G_Y) &= (X' \lor X \lor G_X) \land (Y' \lor Y \lor G_Y) \\ \mathsf{G}_{Z}^{\mathsf{AND}}(X', X, G_X, Y', Y, G_Y) &= (X' \land \bar{X} \land \bar{Y}' \land Y) \lor (\bar{X}' \land X \land Y' \land \bar{Y}) \\ & \lor (G_X \land (Y' \lor Y \lor G_Y)) \lor (G_Y \land (X' \lor X \lor G_X)) \end{aligned}$$

In contrast to the initial version of  $\mathsf{F}_Z^{\mathsf{AND}}$ , the revised version integrates the additional constraint that a signal remains constantly zero only if it is free of glitches. Adhering to a conservative approach, we acknowledge that every glitch occurring on X or Y could potentially provide information to an adversary probing Z. Consequently, the revised version of  $\mathsf{F}_Z^{\mathsf{AND}}$  indicates a probe extension for every glitch detected on X or Y. We adopted the same conservative approach in defining  $\mathsf{G}_Z^{\mathsf{AND}}$ . The first two monomials of  $\mathsf{G}_Z^{\mathsf{AND}}$  address scenarios where a glitch on Z can occur even if X and Y are free of glitches (see  $S_6$  and  $S_9$  in Table 1a). However, if X (or Y) is glitchy, we assume that the glitch propagates to Z unless Y (or X) is constantly zero and free of glitches.

## 4.3 Data-Dependent Probe-Extension of an OR-gate

We continue by examining Table 1b to derive  $F_Z^{OR}$  and  $G_Z^{OR}$ , which represent a probeextension function and a glitch-extension function respectively. These functions aim to model the probe extension through an OR-gate in a less conservative manner compared to the robust *d*-probing model.

Case 1. For  $S_7$ , and  $S_{11}$ - $S_{15}$ , X or Y remains at a constant value of 1. These scenarios lead to a signal waveform for Z that is constantly 1. In particular, if X (resp. Y) is constantly 1 then Z is constantly 1 independent of any toggle on Y (resp. X). Hence, these observations hold true independent of any placement and routing considerations.

Case 2. For  $S_0 X$  and Y remain at a constant value of 0. Hence, due to the underlying logic of the OR-gate,  $S_0$  is the only case where Z is constantly 0. Again, this holds true independent of any placement and routing considerations.

Case 3. For  $S_1 - S_2$ ,  $S_4 - S_5$ ,  $S_8$ , and  $S_{10}$  either X and Y both toggle from the same stable state to another state state (see  $S_5$  and  $S_{10}$ ) or only X (resp. Y) toggles while Y (resp. X) remains at a constant value of 0. Consequently, the waveform of Z shows the same toggle as the waveform of at least one of the inputs. The observation of a single toggle on Z is not influenced by placement and routing while the exact time of toggle depends on the particular routing of the wires.

Case 4. As for the AND-gate, for  $S_6$  and  $S_9$  X and Y both toggle inversely, potentially resulting in a glitch on Z.

The observations regarding the OR-gate closely resemble the findings discussed earlier concerning the AND-gate. Specifically, for the scenarios outlined in *Case* 1, the assumptions made by the robust *d*-probing model are too conservative while they are valid for *Cases* 2-4. Therefore, the probe-extension function  $\mathbb{F}_Z^{OR} : \mathbb{F}_2^4 \to \mathbb{F}_2$  for the output *Z* of an OR-gate over its consecutive input states  $X', X, Y', Y \in \mathbb{F}_2$  must be defined in a way that the probe-extension stops all all scenarios outlined in *Case* 1 and otherwise continues. We show a possible equation for  $\mathbb{F}_Z^{OR}$  in Equation 2 under the assumption that there are no glitches on *X* or *Y*.

$$\mathsf{F}_{Z}^{\mathsf{OR}}(X', X, Y', Y) = (\bar{X}' \lor \bar{X}) \land (\bar{Y}' \lor \bar{Y}) \tag{2}$$

Contrary to Equation 1, Equation 2 does only return 0 if at least one of the inputs stays at constant 1, i.e. X' = 1 and X = 1 or Y' = 1 and Y = 1. For all other input vectors, Equation 2 returns 1 indicating that a robust probe  $P_Z^{\text{robust}}$  must be extended to two robust probes  $P_X^{\text{robust}}$  and  $P_Y^{\text{robust}}$ .

#### 4.4 Data-Dependent Glitch-Propagation of an OR-Gate

To account for glitches on X and Y, the inputs of an OR-gate, we introduce another glitchpropagation function  $G_Z^{OR} : \mathbb{F}2^6 \to \mathbb{F}_2$  for the output Z of an OR-gate across its consecutive inputs X', X, Y', Y, along with two variables  $G_X$  and  $G_Y$  indicating the presence of a glitch on X or Y respectively. Additionally, we revise  $\mathbb{F}_Z^{OR} : \mathbb{F}2^6 \to \mathbb{F}_2$  to accommodate glitches on X and Y.

$$\begin{aligned} \mathsf{F}_{Z}^{\mathsf{OR}}(X', X, G_X, Y', Y, G_Y) &= (\bar{X}' \lor \bar{X} \lor G_X) \land (\bar{Y}' \lor \bar{Y} \lor G_Y) \\ \mathsf{G}_{Z}^{\mathsf{OR}}(X', X, G_X, Y', Y, G_Y) &= (X' \land \bar{X} \land \bar{Y}' \land Y) \lor (\bar{X}' \land X \land Y' \land \bar{Y}) \\ &\lor (G_X \land (\bar{Y}' \lor \bar{Y} \lor G_Y)) \lor (G_Y \land (\bar{X}' \lor \bar{X} \lor G_X)) \end{aligned}$$

Now,  $F_Z^{OR}$  stops the probe-extension only if at least one of the inputs remains constant at 1 and is free from glitches simultaneously. Put differently, any glitch occurring on X or Y triggers probe-extension.  $G_Z^{OR}$  is build in the same way as  $G_Z^{AND}$ . The first two monomials of  $G_Z^{OR}$  address scenarios where a glitch on Z can occur even if X and Y are free of glitches (see  $S_6$  and  $S_9$  in Table 1b). However, if X (or Y) is glitchy, we assume that the glitch propagates to Z unless Y (or X) is constantly one and free of glitches.

## 4.5 Other Gates

While we have introduced the concept of data-dependent probe and glitch propagation using the AND- and OR-gates as examples, we remark that the same principle can be applied to derive equivalent functions for other gates with a fan-in of two, such as NAND, NOR, XOR, and XNOR, in a straightforward manner. The corresponding results for these gates are provided in the appendix. However, the NOT-gate, which takes one input X and produces one output Z, is treated differently. This is because every consecutive input is directly observable through the output Z. Consequently, for a NOT-gate, two key observations hold: (1) there exists no scenario where probe propagation should stop at Z, and (2) every glitch occurring on X propagates to Z. Formally, this implies that the probe- and glitch-propagation functions return 1 for every possible input. To maintain simplicity, we opt not to define such functions explicitly and instead assume that a robust probe  $P_Z^{\text{robust}}$  is replaced directly by a robust probe  $P_X^{\text{robust}}$ , aligning with the principles of the robust d-probing model.

# 5 The Robust but Relaxed (RR) *d*-Probing Model

Building upon our observations, we introduce the RR *d*-probing model, designed to relax the overly conservative glitch treatment of the robust *d*-probing model. Therefore, we define a new class of probes, referred to as relaxed probes, which are, when placed on the output signal of a combinational gate, conditionally propagated depending on the operation performed by the gate and its processed data. Before extending a relaxed probe  $P_E^{\rm relaxed}$  placed on an arbitrary wire *E*, it is imperative to ensure that all probe-extension and glitch-propagation functions have been evaluated. When evaluating a masked circuit  $\tilde{C}$ , i.e. initializing input gates and sequentially processing gates from input gates to output gates, we initially set  $G_Z = 0$  if Z is the output of an input gate. Subsequently, after evaluating the output of a combinational gate Z, we compute  $G_Z$  and then  $F_Z$  based on the functionality of the gate. Once this step is completed, and the information regarding probe and glitch propagation, i.e. all  $F_E$  and  $G_E$  for every E which is an output of a combinational gate, is available, we proceed with the actual probe-extension procedure. We formalize the relaxed probe-extension procedure, denoted relaxed\_extend, in Algorithm 3.

| Algorithm 3 Relaxed Extension (re | laxed extend) |  |

|-----------------------------------|---------------|--|

|-----------------------------------|---------------|--|

Input:  $P_E^{\text{relaxed}}$  $\triangleright$  Relaxed probe on wire E**Output:** P  $\triangleright$  The set of standard probes 1: if  $P_{E}^{\text{relaxed}}$  is placed on the output of combinational gate with fan in 2 then  $\mathbf{i}\mathbf{f} F_E = 1 \mathbf{then}$ 2:  $\mathbf{P} \leftarrow \{\texttt{relaxed\_extend}(P_X^{\text{relaxed}})\} \cup \{\texttt{relaxed\_extend}(P_Y^{\text{relaxed}})\} \quad \triangleright F_X \text{ and}$ 3:  $F_Y$  denote the relaxed probes on both inputs of the combinational gate else 4:  $\mathbf{P} \leftarrow \{P_{E'}\} \cup \{P_E\}$  $\triangleright$  Do the transition extension 5:end if 6: 7: else if  $P_E^{\text{relaxed}}$  is placed on the output of an NOT-gate then 8:  $\mathbf{P} \leftarrow \texttt{relaxed\_extend}(P_X^{\text{relaxed}}) \triangleright P_X^{\text{relaxed}}$  denotes the relaxed probe on the input of the NOT-gate 9: else if  $P_E^{\text{relaxed}}$  is placed on an output of a sequential gate or a primary input then 10: $\mathbf{P} \leftarrow \{P_{E'}\} \cup \{P_E\}$  $\triangleright$  Do the transition extension 11: end if 12:13: end if

Algorithm 3 conditionally extends  $P_E^{\text{relaxed}}$  based on  $F_E$ , i.e the decision whether a probe should be extended based on the operations and data. If such extension is deemed necessary,  $P_E^{\text{relaxed}}$  gets substituted by relaxed probes on all inputs of the gate computing E. Otherwise,  $P_E^{\text{relaxed}}$  gets directly replaced by two standard probes recording two consecutive states of E without further extension.

## 5.1 An Illustrative Example

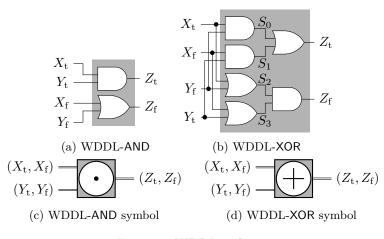

To provide an illustrative example of applying Algorithm 3 to a straightforward yet concrete design, and to support the argumentation for more complex designs, we briefly introduce the basic Wave Dynamic Differential Logic (WDDL)-AND and WDDL-XOR gadgets in Figure 2. We use the style and symbols introduced in [MLM23]. WDDL utilizes Dual-Rail Pre-charge (DRP) logic, where every variable X is represented as a tuple  $(X_t, X_f)$ , with  $X_t = X$  and  $X_f = \bar{X}$ , in a way that it is guaranteed that no glitch can occur within a WDDL-protected circuit.

**Example 2** (WDDL-AND). Consider a WDDL-AND (cf. Figure 2a) with two primary inputs each given in dual-rail representation as  $(X_t, X_f)$  and  $(Y_t, Y_f)$ , and one primary output, also in dual-rail representation,  $(Y_t, Y_f)$ . According to the DRP logic, we assume that the inputs are pre-charged, i.e.  $(X'_t, X'_f, Y'_t, Z'_t, Z'_f) = (0, 0, 0, 0, 0, 0)$  before being set to their final state and that  $(G_{X_t}, G_{X_f}, G_{Y_t}, G_{Y_f}) = (0, 0, 0, 0, 0)$ . Initially, let  $P_{Z_t}^{\text{relaxed}}$  be a relaxed probe placed on  $Z_t$ . Before extending  $P_{Z_t}^{\text{relaxed}}$  by Algorithm 3 we compute  $G_{Z_t}$  and  $F_{Z_t}$  as follows:

$$G_{Z_{\mathsf{t}}} = \mathsf{G}_{Z_{\mathsf{t}}}^{\mathsf{AND}}(X'_{\mathsf{t}}, X_{\mathsf{t}}, G_{X_{\mathsf{t}}}, Y'_{\mathsf{t}}, Y_{\mathsf{t}}, G_{Y_{\mathsf{t}}}) \qquad F_{Z_{\mathsf{t}}} = \mathsf{F}_{Z_{\mathsf{t}}}^{\mathsf{AND}}(X'_{\mathsf{t}}, X_{\mathsf{t}}, G_{X_{\mathsf{t}}}, Y'_{\mathsf{t}}, Y_{\mathsf{t}}, G_{Y_{\mathsf{t}}})$$

Figure 2: WDDL gadgets.

When executing Algorithm 3, the decision to extend  $P_{Z_t}^{\text{relaxed}}$  depends on  $F_{Z_t}$ . We show the concrete extensions for all valid states of  $(X_t, Y_t, Z_t)$  in the following:

$$\begin{aligned} & (X_{t}, Y_{t}, Z_{t}) = (0, 0, 0) & F_{Z_{t}} = 0 & P_{Z_{t}}^{\text{relaxed}} \to \{P_{Z_{t}'}, P_{Z_{t}}\} \\ & (X_{t}, Y_{t}, Z_{t}) = (0, 1, 0) & F_{Z_{t}} = 0 & P_{Z_{t}}^{\text{relaxed}} \to \{P_{Z_{t}'}, P_{Z_{t}}\} \\ & (X_{t}, Y_{t}, Z_{t}) = (1, 0, 0) & F_{Z_{t}} = 0 & P_{Z_{t}}^{\text{relaxed}} \to \{P_{Z_{t}'}, P_{Z_{t}}\} \\ & (X_{t}, Y_{t}, Z_{t}) = (1, 1, 1) & F_{Z_{t}} = 1 & P_{Z_{t}}^{\text{relaxed}} \to \{P_{X_{t}'}, P_{X_{t}}, P_{Y_{t}'}, P_{Y_{t}}\} \end{aligned}$$

As  $G_{Z_t}$  is zero for all valid input sequences, we can conclude that the DRP logic indeed leads to a glitch-free WDDL-AND. However, this does not hold if the gate is not properly pre-charged. For example, it holds that:

$$\begin{aligned} (X'_{\mathsf{t}}, X_{\mathsf{t}}, Y'_{\mathsf{t}}, Z'_{\mathsf{t}}, Z_{\mathsf{t}}) &= (1, 0, 0, 1, 0, 0) \qquad (G_{Z_{\mathsf{t}}}, F_{Z_{\mathsf{t}}}) = (1, 1) \\ P_{Z_{\mathsf{t}}}^{\mathrm{relaxed}} &\to \{P_{X'_{\mathsf{t}}}, P_{X_{\mathsf{t}}}, P_{Y'_{\mathsf{t}}}, P_{Y_{\mathsf{t}}}\} \end{aligned}$$

Now, let  $P_{Z_{\rm f}}^{\rm relaxed}$  be a relaxed probe placed on  $Z_{\rm f}$ . We compute  $G_{Z_{\rm f}}$  and  $F_{Z_{\rm f}}$  as follows:

$$G_{Z_{\mathrm{f}}} = \mathsf{G}_{Z_{\mathrm{f}}}^{\mathsf{OR}}(X_{\mathrm{f}}', X_{\mathrm{f}}, G_{X_{\mathrm{f}}}, Y_{\mathrm{f}}', Y_{\mathrm{f}}, G_{Y_{\mathrm{f}}}) \qquad F_{Z_{\mathrm{f}}} = \mathsf{F}_{Z_{\mathrm{f}}}^{\mathsf{OR}}(X_{\mathrm{f}}', X_{\mathrm{f}}, G_{X_{\mathrm{f}}}, Y_{\mathrm{f}}', Y_{\mathrm{f}}, G_{Y_{\mathrm{f}}})$$

The decision to extend  $P_{Z_{\rm f}}^{\rm relaxed}$  depends on  $F_{Z_{\rm f}}$ . We show the concrete extensions for all valid input states in the following:

| $(X_{\rm f}, Y_{\rm f}, Z_{\rm f}) = (0, 0, 0)$ | $F_{Z_{\mathrm{f}}} = 1$ | $P_{Z_{\mathrm{f}}}^{\mathrm{relaxed}} \to \{P_{X_{\mathrm{f}}'}, P_{X_{\mathrm{f}}}, P_{Y_{\mathrm{f}}'}, P_{Y_{\mathrm{f}}}\}$         |

|-------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| $(X_{\rm f}, Y_{\rm f}, Z_{\rm f}) = (0, 1, 1)$ | $F_{Z_{\rm f}} = 1$      | $P_{Z_{\mathrm{f}}}^{\mathrm{relaxed}} \rightarrow \{P_{X_{\mathrm{f}}'}, P_{X_{\mathrm{f}}}, P_{Y_{\mathrm{f}}'}, P_{Y_{\mathrm{f}}}\}$ |

| $(X_{\rm f}, Y_{\rm f}, Z_{\rm f}) = (1, 0, 1)$ | $F_{Z_{\rm f}} = 1$      | $P_{Z_{\mathrm{f}}}^{\mathrm{relaxed}} \rightarrow \{P_{X_{\mathrm{f}}'}, P_{X_{\mathrm{f}}}, P_{Y_{\mathrm{f}}'}, P_{Y_{\mathrm{f}}}\}$ |

| $(X_{\rm f}, Y_{\rm f}, Z_{\rm f}) = (1, 1, 1)$ | $F_{Z_{\mathrm{f}}} = 1$ | $P_{Z_{\mathrm{f}}}^{\mathrm{relaxed}} \to \{P_{X_{\mathrm{f}}'}, P_{X_{\mathrm{f}}}, P_{Y_{\mathrm{f}}'}, P_{Y_{\mathrm{f}}}\}$         |

**Example 3** (WDDL-XOR). Consider a WDDL-XOR (cf. Figure 2b) with two primary inputs each given in dual-rail representation as  $(X_t, X_f)$  and  $(Y_t, Y_f)$ , and one primary output, also in dual-rail representation,  $(Y_t, Y_f)$ . According to the DRP logic, we assume that the inputs are pre-charged, i.e.  $(X_{t'}, X_{f'}, Y_t', S_0, S_1, S_2, S_3, Z_t', Z_f') = (0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0)$  before being set to their final state and that  $(G_{X_t}, G_{X_f}, G_{S_0}, G_{S_1}, G_{S_2}, G_{S_3}, G_{Y_t}, G_{Y_f}) = (0, 0, 0, 0, 0, 0, 0, 0)$ . Let  $P_{Z_t}^{\text{relaxed}}$  (resp.  $P_{Z_f}^{\text{relaxed}}$ ) be a relaxed probe placed on  $Z_t$  (resp.

$Z_{\rm f}$ ). Here, we start by computing  $(G_{S_0}, G_{S_1}, G_{S_2}, G_{S_3})$  followed by  $(F_{S_0}, F_{S_1}, F_{S_2}, F_{S_3})$  as:

$$\begin{split} & G_{S_0} = \mathsf{G}_{S_0}^{\mathsf{AND}}(X'_{\mathsf{t}}, X_{\mathsf{t}}, G_{X_{\mathsf{t}}}, Y'_{\mathsf{f}}, Y_{\mathsf{f}}, G_{Y_{\mathsf{f}}}) \quad F_{S_0} = \mathsf{F}_{S_0}^{\mathsf{AND}}(X'_{\mathsf{t}}, X_{\mathsf{t}}, G_{X_{\mathsf{t}}}, Y'_{\mathsf{f}}, Y_{\mathsf{f}}, G_{Y_{\mathsf{f}}}) \\ & G_{S_1} = \mathsf{G}_{S_1}^{\mathsf{AND}}(X'_{\mathsf{f}}, X_{\mathsf{f}}, G_{X_{\mathsf{f}}}, Y'_{\mathsf{t}}, Y_{\mathsf{t}}, G_{Y_{\mathsf{t}}}) \quad F_{S_1} = \mathsf{F}_{S_1}^{\mathsf{AND}}(X'_{\mathsf{f}}, X_{\mathsf{f}}, G_{X_{\mathsf{f}}}, Y'_{\mathsf{t}}, Y_{\mathsf{t}}, G_{Y_{\mathsf{t}}}) \\ & G_{S_2} = \mathsf{G}_{S_2}^{\mathsf{OR}}(X'_{\mathsf{t}}, X_{\mathsf{t}}, G_{X_{\mathsf{t}}}, Y'_{\mathsf{f}}, Y_{\mathsf{f}}, G_{Y_{\mathsf{f}}}) \quad F_{S_2} = \mathsf{F}_{S_2}^{\mathsf{OR}}(X'_{\mathsf{t}}, X_{\mathsf{t}}, G_{X_{\mathsf{t}}}, Y'_{\mathsf{f}}, Y_{\mathsf{f}}, G_{Y_{\mathsf{f}}}) \\ & G_{S_3} = \mathsf{G}_{S_3}^{\mathsf{OR}}(X'_{\mathsf{f}}, X_{\mathsf{f}}, G_{X_{\mathsf{f}}}, Y'_{\mathsf{t}}, Y_{\mathsf{t}}, G_{Y_{\mathsf{t}}}) \quad F_{S_3} = \mathsf{F}_{S_3}^{\mathsf{OR}}(X'_{\mathsf{f}}, X_{\mathsf{f}}, G_{X_{\mathsf{f}}}, Y'_{\mathsf{t}}, Y_{\mathsf{t}}, G_{Y_{\mathsf{t}}}) \end{split}$$

Next,  $(G_{S_0}, G_{S_1}, G_{S_2}, G_{S_3})$  is used to compute  $(G_{Z_t}, G_{Z_f})$  and  $(F_{Z_t}, F_{Z_f})$  as:

$$\begin{split} G_{Z_{t}} &= \mathsf{G}_{Z_{t}}^{\mathsf{OR}}(S'_{0}, S_{0}, G_{S_{0}}, S'_{1}, S_{1}, G_{S_{1}}) \qquad F_{Z_{t}} = \mathsf{F}_{Z_{t}}^{\mathsf{OR}}(S'_{0}, S_{0}, G_{S_{0}}, S'_{1}, S_{1}, G_{S_{1}}) \\ G_{Z_{f}} &= \mathsf{G}_{Z_{f}}^{\mathsf{AND}}(S'_{2}, S_{2}, G_{S_{2}}, S'_{3}, S_{3}, G_{S_{3}}) \quad F_{Z_{f}} = \mathsf{F}_{Z_{f}}^{\mathsf{AND}}(S'_{2}, S_{2}, G_{S_{2}}, S'_{3}, S_{3}, G_{S_{3}}) \end{split}$$

When executing Algorithm 3, the decision to extend  $P_{Z_t}^{\text{relaxed}}$  now depends on  $(F_{S_0}, F_{S_1}, F_{Z_t})$  while the extension of  $P_{Z_f}^{\text{relaxed}}$  depends on  $(F_{S_2}, F_{S_3}, F_{Z_f})$ . We show the concrete extensions for all valid input states in Table 2 and Table 3.

Table 2: Results from Algorithm 3 with  $P_{Z_t}^{\text{relaxed}}$  depending on the input state.

| $(X_{\mathrm{t}}, X_{\mathrm{f}}, Y_{\mathrm{t}}, Y_{\mathrm{f}}, S_0, S_1, Z_{\mathrm{t}})$ | $\left(F_{S_0}, F_{S_1}, F_{Z_t}\right)$ | $P_{Z_{\mathrm{t}}}^{\mathrm{relaxed}}$                               |

|----------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------|

| $\left(0,1,0,1,0,0,0 ight)$                                                                  | (0, 0, 0)                                | $\{P_{Z'_{t}}, P_{Z_{t}}\}$                                           |

| $\left(0,1,1,0,0,1,1 ight)$                                                                  | (0,1,1)                                  | $\{P_{S'_0}, P_{S_0}, P_{X'_{f}}, P_{X_{f}}, P_{Y'_{t}}, P_{Y_{t}}\}$ |

| $\left(1,0,0,1,1,0,1 ight)$                                                                  | (1,0,1)                                  | $\{P_{S_1'}, P_{S_1}, P_{X_t'}, P_{X_t}, P_{Y_f'}, P_{Y_f}\}$         |

| (1, 0, 1, 0, 0, 0, 0)                                                                        | (0, 0, 0)                                | $\{P_{Z'_{t}}, P_{Z_{t}}\}$                                           |

Table 3: Results from Algorithm 3 with  $P_{Z_f}^{\text{relaxed}}$  depending on the input state.

| $(X_{\mathrm{t}}, X_{\mathrm{f}}, Y_{\mathrm{t}}, Y_{\mathrm{f}}, S_2, S_3, Z_{\mathrm{f}})$ | $\left(F_{S_2}, F_{S_3}, F_{Z_{\rm f}}\right)$ | $P_{Z_{\mathrm{f}}}^{\mathrm{relaxed}}$                                                                        |

|----------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| (0, 1, 0, 1, 1, 1, 1)                                                                        | (1, 1, 1)                                      | $\{P_{X'_{t}}, P_{X_{t}}, P_{X'_{f}}, P_{X_{f}}, P_{Y'_{t}}, P_{Y_{t}}, P_{Y'_{f}}, P_{Y'_{f}}, P_{Y'_{f}}\}$  |

| (0, 1, 1, 0, 0, 1, 0)                                                                        | (0,1,0)                                        | $\{P_{Z'_{\mathrm{f}}}, P_{Z_{\mathrm{f}}}\}$                                                                  |

| (1, 0, 0, 1, 1, 0, 0)                                                                        | (1,0,0)                                        | $\{P_{Z_{\mathrm{f}}'},P_{Z_{\mathrm{f}}}\}$                                                                   |

| $\left(1,0,1,0,1,1,1 ight)$                                                                  | (1, 1, 1)                                      | $\{P_{X'_{t}}, P_{X_{t}}, P_{X'_{f}}, P_{X'_{f}}, P_{Y'_{t}}, P_{Y_{t}}, P_{Y'_{f}}, P_{Y'_{f}}, P_{Y'_{f}}\}$ |

#### 5.2 Security Notions

Building upon the probe-extension described in Algorithm 3 we introduce definitions for probing security (see Definition 6) and PINI (see Definition 7) within the RR *d*-probing model. Consequently, we denote an adversary capable of placing a maximum of *d* relaxed probes on arbitrary wires of  $\tilde{C}$  as RR *d*-probing adversary.

**Definition 6** (RR *d*-Probing Security). A masked circuit  $\tilde{C}$  with secret input **X** is RR *d*-probing secure iff for any set of relaxed probes **P**, with  $|\mathbf{P}| \leq d$ , the joint distribution over all observations **Q** made by the relaxed probes is statistically independent of **X**

**Definition 7** (RR *d*-Probe-Isolating Non-Interference (PINI)). Let  $\tilde{\mathbf{C}}$  be a masked circuit with secret input  $\mathbf{X}$ . Further, let  $\mathbf{P}_{\mathrm{I}}$  be a set of relaxed probes on internal wires of  $\tilde{\mathbf{C}}$  with  $|\mathbf{P}_{\mathrm{I}}| = t_1$  and  $\mathbf{I}_{\mathrm{O}}$  be the set of indices assigned to the relaxed probes on output wires in the set  $\mathbf{P}_{\mathrm{O}}$  with  $|\mathbf{I}_{\mathrm{O}}| = t_2$ .  $\tilde{\mathbf{C}}$  is relaxed *d*-PINI iff for every  $\mathbf{P} = \mathbf{P}_{\mathrm{I}} \cup \mathbf{P}_{\mathrm{O}}$  with  $t_1 + t_2 \leq d$ , there exists a set of indices  $\mathbf{I}_{\mathrm{I}}$  with  $|\mathbf{I}_{\mathrm{I}}| \leq t_1$  such that  $\mathbf{P}$  is perfectly simulatable from  $\mathbf{S} = \tilde{\mathbf{X}}^{\mathbf{I}_{\mathrm{I}} \cup \mathbf{I}_{\mathrm{O}}}$ .

## 5.3 Relation to Other Probing Models

Having introduced a new model, it is essential to establish its relationship with previously discussed models, specifically the d-probing model and the robust d-probing model. To achieve this, we define two new probe-extension functions:  $F^0$  and  $F^1$ . It holds that  $F^0$  constantly returns 0 independent of the underlying gate and data while  $F^1$  constantly returns 1 in the same manner. Based on  $F^0$  and  $F^1$  we formalize the relation between the RR *d*-probing model and the *d*-probing model (resp. robust *d*-probing model) in Lemma 1 (resp. Lemma 2).

**Lemma 1.** The RR d-probing model with probe-extension function  $F^0$  is equivalent to the *d*-probing model.

We remark that  $\mathsf{F}^0$  implies no probe-extension, i.e. a relaxed probe  $P_E^{\mathrm{relaxed}}$  on E is directly replaced by a standard probe<sup>4</sup>  $P_E$  on E if the probe-extension is performed based on  $\mathsf{F}^0$  what is equivalent to placing d standard probes on arbitrary wires as suggested by the d-probing model.

**Lemma 2.** The RR d-probing model with probe-extension function  $F^1$  is equivalent to the robust d-probing model.

Analogously,  $\mathsf{F}^1$  implies a full probe-extension, i.e. a relaxed probe  $P_E^{\mathrm{relaxed}}$  on E is extended backwards until a primary input or output of a sequential gate is reached. This corresponds to the probe-extension described in Algorithm 2 which is related to the robust *d*-probing model. As the probe-extension functions applied in Algorithm 3 conditionally return 0 or 1, we positioned our model between the *d*-probing model and the robust *d*-probing model. Hence, it holds that (1) every RR *d*-probing secure circuit is also *d*-probing secure (but not vice versa) and (2) every robust *d*-probing secure circuit is also RR *d*-probing secure (but not vice versa).

# 6 Tool-Assisted Evaluation

To automate the evaluation of arbitrary masked circuits, given as a gate-level netlist, we developed an extension of the PROLEAD tool which allows to verify *d*-probing security based on our new model. PROLEAD synergistically merges the advantages of formal verification, offering verification under well-defined adversary models, with leakage simulation, renowned for its efficiency. This integrated framework currently assesses *d*-probing security within the robust probing model by simulating intermediate signals within the target hardware circuit. Thanks to this approach, PROLEAD can analyze circuits that fall beyond the scope of existing formal verification tools, such as a fully masked AES core, with sufficient accuracy. Below, we focus on the adjustments we made to PROLEAD to encompass leakage evaluation under the RR *d*-probing model.

## 6.1 Extraction of Relevant Wires

When evaluating a masked circuit under the robust d-probing model, it suffices to focus exclusively on robust probes on primary outputs and inputs of sequential gates, denoted by a set of, so-called, relevant wires **H**:

$\mathbf{H} = \{ E \in \mathbf{E} | E \text{ is the input of a sequential gate or output gate} \}$

Robust probes placed on other wires consistently provide less information than a robust probe in  $\mathbf{H}$ . This property is for example checked in Algorithm 1 of [MM22] to extract  $\mathbf{H}$ .

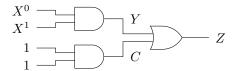

Figure 3: Exemplary circuit with constant inputs

To discuss the selection of relevant wires for the evaluation under the RR d-probing model we analyze the exemplary (masked) circuit depicted in Figure 3.

We assume that a secret input  $X \in \mathbb{F}_2$  is represented as two shares  $X^0, X^1$  satisfying  $X = X^0 \oplus X^1$ . Both shares serve as primary inputs while all other primary inputs are constantly kept at 1. Now, let  $P_Z^{\text{relaxed}}$  be a relaxed probe on the primary output Z. As one input of the OR-gate is constantly set to 1,  $P_Z^{\text{relaxed}}$  gets not extended further but is instead replaced by two standard probes  $P_{Z'} = 1$  and  $P_Z = 1$ . The joint distribution made by  $P_{Z'}$  and  $P_Z$  is statistically independent of X. Consequently, if we only consider  $P_Z^{\text{relaxed}}$  this circuit will be reported as RR 1-probing secure. However, let  $P_Y^{\text{relaxed}}$  be a relaxed probe on Y which remains unaffected by the primary inputs constantly set to 1. Hence,  $P_Y^{\text{relaxed}}$  gets extended, in some cases, to the primary inputs  $X^0$  and  $X^1$  ultimately resulting in a set of standard probes  $\mathbf{P} = \{P_{X^{0'}}, P_{X^0}, P_{X^{1'}}, P_{X^1}\}$  effectively violating the RR 1-probing security. Therefore, relaxed probes must be placed on all wires of the circuit increasing the number of sets of relaxed probes to  $\binom{|\mathbf{E}|}{d}$ , compared to the number of sets of relaxed probes to  $\binom{|\mathbf{E}|}{d}$ , compared to the number of sets of relaxed probes d. Technically, we adjusted Algorithm 1 of [MM22] to include every wire in the set of relevant wires.

## 6.2 Probe-Extension

Unlike the probe extension of the original PROLEAD version, which involves executing Algorithm 5 of [MM22], the probe extension for the RR *d*-probing model relies on the processed data, namely the simulations generated by PROLEAD. Thus, a direct replacement of Algorithm 5 with our probe-extension procedure, as formalized in Algorithm 3, is not possible. The rationale behind this is that, for the robust d-probing model, PRO-LEAD precomputes the probe extensions for all  $E \in \mathbf{H}$  because the probe extension is independent of the processed data. However, this independence does not hold for the relaxed-robust probing model. As a result, we must compute the probe extension for every execution simulated by PROLEAD, which significantly increases the runtime dedicated to the evaluation process. To accomplish this efficiently, we extended PROLEAD's simulation routine to compute a triple  $(E, G_E, F_E) \in \mathbb{F}_2^3$  for every wire E serving as an output of a combinational gate, employing a bit-sliced approach. Technically, this incurs an overhead equivalent to evaluating the circuit three times, effectively tripling both the simulation runtime and the memory required to store the circuit's state. Further, when dealing with the RR *d*-probing model we precompute a simplified version of Algorithm 5 of [MM22] just to get the maximum of standard probes  $n_{max}$  after the probe extension while integrating the actual data-dependent probe extension into the distribution-update routine.

#### 6.3 Update Distributions

The original version of PROLEAD generates a distribution table for every set of standard probes  $\mathbf{P}$  with  $|\mathbf{P}| = n_{max}$  derived from extending up to *d* robust probes. Subsequently,

$<sup>^4\</sup>mathrm{For}$  the sake of simplicity, we ignore the transition-extension in our argumentation.

PROLEAD evaluates the distribution table by using a statistical hypothesis test. Specifically, for each simulation PROLEAD generates the observation set  $\mathbf{Q}$  with  $|\mathbf{Q}| = n_{max}$  by replacing every standard probe in  $\mathbf{P}$  with its corresponding simulated state. Afterwards, the distribution table, counting how often a particular observation occurs, gets updated by  $\mathbf{Q}$ . As already explained, we generate  $\mathbf{P}$ , derived from extending relaxed probes, for every simulation individually, with  $n \leq n_{max}$  varying accordingly which is shown in Line 4 of Algorithm 5. However, PROLEAD's contingency tables are structured such that they can only accommodate updates with observation sets of equal size. To achieve this, we pad every  $\mathbf{Q}$  with trailing zeros such that  $|\mathbf{Q}| = n$  becomes  $n_{max}$ . Unfortunately, this leads to another problem which we demonstrate by a practical example shown in Example 4.

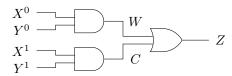

**Example 4.** Consider the exemplary circuit shown in Figure 4 and a relaxed probe  $P_Z^{\text{relaxed}}$ .

Figure 4: Exemplary circuit

Applying, the probe-extension on  $P_Z^{\text{relaxed}}$  may result in a set of standard probes **P** such that  $\mathbf{P} = \{P_{X^{0'}}, P_{X^0}, P_{X^{1'}}, P_{X^1}, P_{Y^{0'}}, P_{Y^0}, P_{Y^{1'}}, P_{Y^1}\}$  which also leads to  $n_{max} = 8$ . However, as we sort **P** in order to remove duplicates, it can be the case that two equal observation sets are derived although the underlying standard probes differ. To illustrate this, we consider two sorted sets, here and in the following denoted by square brackets, of standard probes, both ultimately resulting in  $\mathbf{Q} = [0, 0, 0, 1, 0, 1, 0, 0]$ .

$$\mathbf{P}_{0} = [P_{X^{0'}}, P_{X^{0}}, P_{Y^{0'}}, P_{Y^{0}}, P_{C'}, P_{C}], F_{Z} = 1, F_{W} = 1, F_{C} = 0$$

$$\mathbf{P}_{1} = [P_{X^{1'}}, P_{X^{1}}, P_{Y^{1'}}, P_{Y^{1}}, P_{W'}, P_{W}], F_{Z} = 1, F_{W} = 0, F_{C} = 1$$

Hence, the contingency table will falsely consider both observations as equal even if the observation relate to different variables.

To distinguish between equal observations in the contingency table, we track the probeextension variables similar to the probes themselves. The ensuing procedure is delineated in Algorithm 4. Basically, Algorithm 4 returns a set of probe-extension variables **F** arranged in the order they are assessed during the probe-extension. Afterwards, the observation set is appended to **F**. Applied to Example 4 this implies that  $\mathbf{Q} = [0, 0, 0, 1, 0, 1, 0, 0]$  will be extended to two distinct observation sets, namely  $\mathbf{Q}_0 = [1, 1, 0, 0, 0, 0, 1, 0, 1, 0, 0]$  and  $\mathbf{Q}_1 = [1, 0, 1, 0, 0, 0, 1, 0, 1, 0, 0]$ . Consequently, both sets become distinguishable.

The final procedure for generating the observation set is outlined in Algorithm 5. Essentially, Algorithm 5 iterates through all relaxed probes placed by an adversary and appends all standard probes derived through the probe extension to a global set of standard probes  $\mathbf{P}$  in Line 4. Similarly, the sequence of all accessed probe-extension variables in generated in Line 5. Subsequently, we remove all duplicates in  $\mathbf{P}$  in Line 7 and concatenate both sets to form the final observation set.

# 7 Case Studies

In the following, we demonstrate the versatility of the RR *d*-probing model, both in formal proofs and its seamless integration into PROLEAD for tool-assisted evaluation. However,

Algorithm 4 Get Probe-Extension Variables (get\_probe\_prop)

| 8                                                                                                |                                                                |

|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Input: $F_E$                                                                                     | $\triangleright$ probe-extension variable of wire $E$          |

| Output: F                                                                                        | ▷ The set probe-extension variables                            |

| 1: if $E$ is the output of a combinational gate                                                  | e with fan in 2 <b>then</b>                                    |

| 2: $\mathbf{F} \leftarrow [\mathbf{F}, F_E]$                                                     |                                                                |

| 3: <b>if</b> $F_E = 1$ <b>then</b>                                                               |                                                                |

| 4: $\mathbf{F} \leftarrow [\mathbf{F}, \mathtt{get\_probe\_prop}(F_X), \mathtt{get}]$            | t_probe_prop $(F_Y)$ ] $\triangleright$ $F_X$ and $F_Y$ denote |

| the probe-extension variables of both inpu                                                       | its of the combinational gate                                  |

| 5: end if                                                                                        |                                                                |

| 6: else if $E$ the output of an NOT-gate the                                                     | n                                                              |

| 7: $\mathbf{F} \leftarrow [\mathbf{F}, \mathtt{get\_probe\_prop}(F_X)] \triangleright F_X$       | denotes the probe-extension variable of the                    |

| the NOT-gate input                                                                               |                                                                |

| 8: end if                                                                                        |                                                                |

|                                                                                                  |                                                                |

| Algorithm 5 Observation Generation                                                               |                                                                |

| Input: $\mathbf{P}^{\text{relaxed}}$                                                             | $\triangleright$ The set of relaxed probes                     |

| Output: Q                                                                                        | $\triangleright$ The observed variables                        |

| 1: $\mathbf{P} \leftarrow \emptyset$                                                             |                                                                |

| 2: $\mathbf{F} \leftarrow \emptyset$                                                             |                                                                |

| 3: for $\forall P_E^{\text{relaxed}} \in \mathbf{P}^{\text{relaxed}}$ do                         |                                                                |

| 4: $\mathbf{P} \leftarrow [\mathbf{P}, \texttt{relaxed}\_\texttt{extend}(P_E^{\text{relaxed}})]$ |                                                                |

| 5: $\mathbf{F} \leftarrow [\mathbf{F}, \mathtt{get\_probe\_prop}(F_E)]$                          |                                                                |

|                                                                                                  |                                                                |

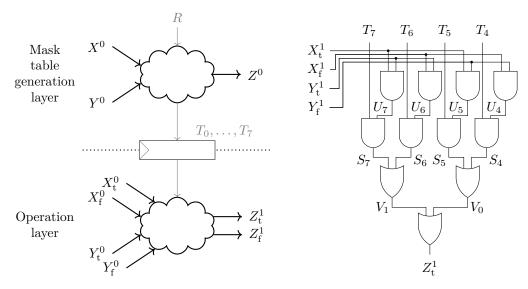

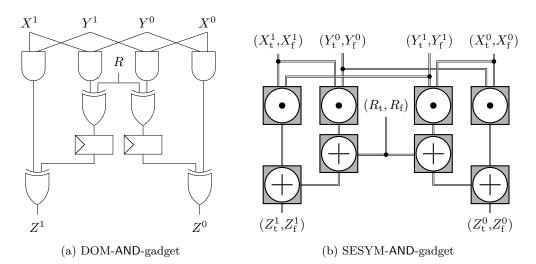

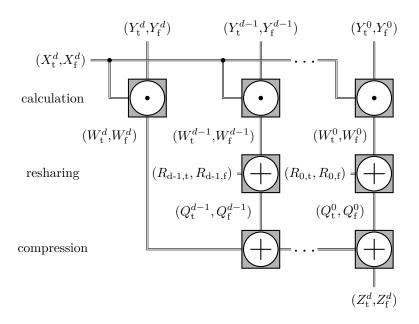

due to the shortage of sound masking schemes claiming security but without being robust d-probing secure, we focus on the schemes analyzed in [MLM23], specifically LMDPL [LMW14] and SESYM [NGPM22], both introduced at CHES. Both schemes utilize DRP logic, where every variable X is represented as a tuple  $(X_t, X_f)$ , with  $X_t = X$  and  $X_f = \bar{X}$ , in a way that it is guaranteed that no glitch can occur within a LMDPL or SESYM-masked circuit. However, proving the security of either LMDPL or SESYM under the robust d-probing model would disregard this glitch-free characteristic, rendering both schemes insecure. Nevertheless, the introduced RR d-probing model acknowledges that LMDPL and SESYM-masked circuits. Therefore, our focus lies in providing the missing details outlined in [MLM23], specifically regarding the formal security (or insecurity) and composability proofs of LMDPL and SESYM within the RR d-probing model.

## 7.1 Setup

6: end for

8:  $\mathbf{Q} \leftarrow [\mathbf{F}, \mathbf{P}]$

7:  $\mathbf{P} \leftarrow \texttt{sort}$  and remove  $\texttt{duplicates}(\mathbf{P})$