# Long Paper CrISA-X: Unleashing Performance Excellence in Lightweight Symmetric Cryptography for Extendable and Deeply Embedded Processors

Oren Ganon<sup>1</sup> and Itamar Levi<sup>1</sup>

Bar-Ilan University, Ramat-Gan, Israel. Emails: oren.ganon@biu.ac.il, itamar.levi@biu.ac.il

#### 1 ABSTRACT

The selection of a Lightweight Cryptography (LWC) algorithm is crucial for resource-limited applications. The National Institute of Standards and Technology (NIST) leads this process, which involves a thorough evaluation of the algorithms' cryptanalytic strength. Furthermore, careful consideration is given to factors such as algorithm latency, code size, and hardware implementation area. These factors are critical in determining the overall performance of cryptographic solutions at edge devices.

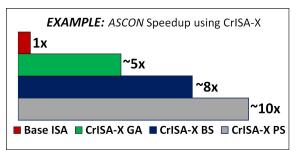

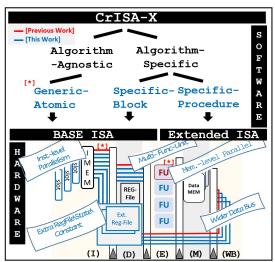

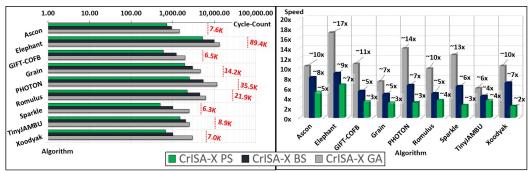

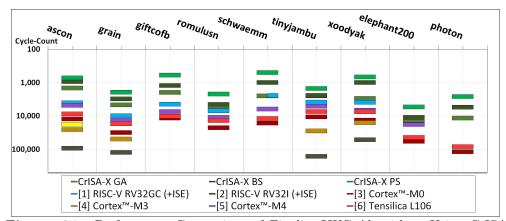

Introducing CrISA-X, a Cryptography Instruction Set Architecture eXtensions designed to improve cryptographic latency on extendable processors. CrISA-X, classified as Generic-Atomic, Block-Specific and Procedure-Specific, leverages RISC processor hardware and a base ISA to effectively execute LWC algorithms. Our study aims to evaluate the execution efficiency of new single-cycle instruction extensions and tightly coupled multicycle instructions on extendable modular RISC processors. CrISA-X provides enhanced speed of various algorithms simultaneously while optimizing ISA adaptability, a feat yet to be accomplished. The extension, diverse for several computation levels, is first specifically tailored for individual algorithms and sets of LWC algorithms, depending on performance, frequency, and area trade-offs. By diligently applying the Min-Max optimization technique, we have configured these extensions to achieve a delicate balance between performance, area code size, etc. Our study presents empirical evidence of the performance enhancement achieved on a real synthesis modular RISC processor. We offer a framework for creating optimized processor hardware and ISA extensions. The CrISA-X framework generally outperforms ISA extensions by delivering significant performance boosts between 3x to 17x while experiencing a relative area cost increase of +12% and +47% in LUTs, in respect to the instruction set category. Notably, as one important example, the utilization of the ASCON algorithm yields a 10x performance boost in contrast to the base ISA instruction implementation.

#### 2 Introduction

The Internet of Things (IoT), Artificial Intelligence of Things (AIoT), and machine-to-machine (M2M) edge devices refer to a vast network of devices connected to the internet, all of which collect, share, and process large amounts of data [BS11]. With the increasing demand for edge computing, the risk of serious security incidents also rises, making it crucial to ensure the security of these systems.

Symmetric-key lightweight cryptography algorithms used on edge devices for data encryption and decryption are designed to be effective and efficient. NIST began a public competition in 2013 to select an authenticated encryption and hashing scheme suitable for such devices on constrained environments [TMC $^+$ 21, MAA $^+$ 20]. In 2021, NIST announced ten finalists to move to the final round of the standardisation process,

Figure: 1. Example of Enhancing ASCON Performance with CrISA-X: A Comparative Latency Analysis of Base ISA Instruction (Baseline) vs. Replacement Code

as shown in Table 1. The finalists include ASCON, Elephant, GIFT-COFB, Grain128-AEAD, ISAP, Photon-Beetle, Romulus, Sparkle, TinyJambu, Xoodyak. In 2023, it was announced that the Ascon family had been chosen to standardize lightweight cryptography. This selection is expected to have significant implications for the cybersecurity industry and represents a major milestone in the field of cryptography. Along with the NIST competition, the CAESAR committee also launched a contest to discover authenticated encryption methods appropriate for devices with limited resources. As part of the CAESAR portfolio for lightweight applications, Ascon is the top selection, while Acron is the second choice. All finalists and selected candidates are potential candidates for edge computing, especially the selected candidates. Clearly, on lightweight nodes performance is a crucial factor in the evaluation process. Parameters such as cycle-count performance, area, and footprint were specifically emphasised, focusing on candidates who performed significantly better than the current NIST standards. To facilitate the deployment of LWC on edge computing environments with constrained resources, ongoing research endeavors to explore diverse approaches to accelerate algorithms [XJL<sup>+</sup>19, SR20]. There are several reasons why it is important to speed up the execution of lightweight cryptography algorithms on processors in edge device applications: lightweight cryptography involves computation in repeated rounds, causing significant latency for encryption, decryption, and hashing (Tag-compression) of each data set. Speeding up these computational blocks can enable the processing of larger encryption data on these devices without sacrificing performance or battery life. Endpoint sensor applications are prime examples of edge devices that perform lightweight encryption as part of the root of trust (RoT) zone. These devices rely on a general-purpose processor to collect sensing data, process it, and execute cryptographic algorithms. Then, the data is transmitted through a secure channel. Crypto processing might limit effective communication speed, reducing the sensor reading rate thus reducing user experience and system effectiveness.

While lightweight cryptography schemes are necessary to reduce latency and resources, endpoint device system designers require processor acceleration features to reduce latency even further [GPKT09, DFA+20]. This allows devices to operate with much higher data throughput. Cryptography encryption mechanisms in processor-based edge devices can be implemented through optimised software libraries written in C language or assembly or through dedicated hardware accelerators. The software approach is flexible but unsuitable for low-frequency constrained devices with strict latency requirements. Dedicated off-processor hardware accelerators often perform better, on the other side of the scale. However, they require more hardware space and are less flexible than software solutions. Moreover, delay caused by transferring data from the processor to the accelerator could also overshadow the benefits of dedicated hardware, depending on the frequency and amount of data being transferred. As a result, there is a growing emphasis on developing processor-based mechanisms, such as custom-specific instructions, that enable efficient encryption while maintaining low-latency requirements and keeping reusability and flexibility.

Researchers exploring this domain are looking specifically at one vector of leveraging the processor's basic ISA and supplementing it with additional instructions to encapsulate a certain amount of computation [MB20, VVP+16, TMC+23, Sab23, GS22]. However, to gain a quantitative understanding of how additional extended instructions, with various levels of computation, can improve the speed and reduce memory costs, it is necessary to tighten the instruction extension together with extended processors and associated hardware. This study aims to explore the potential of instruction extension with any extendable RISC processor, such as the RISC-V open standard ISA, to enhance the performance of lightweight cryptographic algorithms. The paper provides technical details regarding the implementation process, which includes the design and development of new instructions, their integration with processors, and the overall impact on system performance and area. The study's findings have significant implications for accelerating algorithms on RISC processors, providing an efficient solution for LWC.

#### 3 Related Work and Our Contribution

Accelerating cryptographic algorithms using custom instruction-set architectures or hardware/software co-design, have long been considered a potential means of enhancing their computation speed. Although the concept is familiar, limited studies have been conducted on the topic. Specifically, existing research has been divided into three categories: first, efficient implementations of the candidates over standard processor architecture, software-hardware and ISAs; second, works that focus on accelerating only one candidate over simple cores <sup>1</sup>; and lastly, some works aim to jointly optimize a small subset of algorithms with minimal or no adaptation of extended processor architectures.

#### 3.1 Related Work Overview

This section aims to provide an overview of the research related to the topic. It will describe the key findings of the relevant studies conducted by previous researchers Table 2 summarizes the main research conducted in this area. Renner and Pozzobon [RPM22], and Sebastian and Enrico [WYY22] conducted a comprehensive analysis of the final ten ciphers from NIST's lightweight cryptography project. They assessed the efficient software implementation performance of these ciphers on different 32-bit processor platforms with varying architectures and provided valuable insights into their performance characteristics under specific test scenarios. The authors' research can assist developers in establishing a performance baseline for LWC software implementation on micro-controller platforms. Edwards and Forrest [EF96] studied hardware/software codesign as a tightly coupled

<sup>&</sup>lt;sup>1</sup>Referring to a single processing element, limited memory and instruction-level parallelism, and other related features from the architecture designer tool-set

|                           | Table 1. 11101 Live illianst algorithms |                              |  |  |  |  |  |

|---------------------------|-----------------------------------------|------------------------------|--|--|--|--|--|

| Algorithm                 | Variant                                 | Feedback                     |  |  |  |  |  |

| Grain-128AEAD             | AEAD                                    | Stream Cipher                |  |  |  |  |  |

| $\operatorname{GIFTcofb}$ | AEAD                                    | Permutation GIFT-128         |  |  |  |  |  |

| Romulus                   | AEAD,Hash                               | Block Cipher Skinny-128-384+ |  |  |  |  |  |

| ASCONf                    | AEAD,Hash                               | Permutation Ascon-p          |  |  |  |  |  |

| Elephant                  | AEAD                                    | Permutation Keccak-f[m]      |  |  |  |  |  |

| ISAP                      | AEAD                                    | Permutation Keccak-f[m]      |  |  |  |  |  |

| PHOTONbee                 | AEAD,Hash                               | Permutation PHOTON256        |  |  |  |  |  |

| SPARKLE                   | AEAD,Hash                               | Permutation Sparkle          |  |  |  |  |  |

| TinyJAMBU                 | AEAD                                    | Permutation TinyJAMBU        |  |  |  |  |  |

| Xoodyak                   | AEAD,Hash                               | Permutation Xoodoo           |  |  |  |  |  |

Table 1: NIST LWC finalist algorithms

Table 2: Summary of Related Work

Academic Work on Accelerating Cryptography Algorithms using ISA Ext'

| Related<br>Work        | Characteristics $/\#\mathrm{Algos}$ ' | Extendable<br>Processor | Extendable<br>ISA |

|------------------------|---------------------------------------|-------------------------|-------------------|

|                        | Single Algo, Native                   | 64bit,No extend         | Extended          |

| [MPP21]                | C-Code                                | $_{ m HW}$              | RISC-V ISA        |

|                        | All finalist, Native                  | 32bit,No extend         | Extended          |

| $[CGM^+23]$            | C-Code                                | $_{ m HW}$              | RISC-V ISA        |

|                        | All finalist,                         | 32bit,No extend         | Base RISC-V       |

| $[\mathrm{CJL}^{+}20]$ | ASM-Code                              | $_{ m HW}$              | ISA               |

|                        | Several Algos',                       | 32bit,No extend         | Standard ARM      |

| [WYY22]                | Native C-Code                         | $_{ m HW}$              | ISA               |

|                        | All finalist, Native                  | 32bit,No extend         | Standard          |

| [RPM20]                | C-Code                                | $_{ m HW}$              | RISC-V ISA        |

|                        | All finalist, Native                  | 32bit,No extend         | Standard          |

| [RPM22]                | C-Code                                | $_{ m HW}$              | RISC-V ISA        |

|                        | All finalist, Native                  | 32bit,No extend         | Standard TI       |

| [ABCdS <sup>+</sup> 2  | [22] C-Code                           | $_{ m HW}$              | ISA               |

| [AÖ21]                 | Single Algo, Native                   | 32 bit, Partly          | Extended          |

|                        | C-Code                                | extend HW               | RISC-V ISA        |

accelerator to enhance software acceleration. Critical regions are parts of an application where software alone cannot meet performance requirements, necessitating hardwarebased solutions or where implementing specific regions in hardware significantly improves performance. Their research highlights the importance of hardware/software codesign to achieve optimal performance. As the popularity of the RISC-V architecture continues to rise, researchers are exploring ways to efficiently implement LWC algorithms through RISC-V ISA Extensions as co-processors. Two teams, Altınay and Örs [AÖ21], and Steinegger and Primas [SP20] have developed ISA Extensions to speed up Ascon permutation. They have designed dedicated instructions to perform an entire Ascon-p round efficiently in hardware. However, these ISA Extensions are designed to target a single algorithm and require tight integration with a specific processor core. They employ hard-coded registers to store the state and focus on a single data path without instruction or memory-level parallelism. Marshall, Page, and Hung Pham [MPP21] have also developed ISA Extensions to accelerate the ChaCha stream cipher by using a similar approach of dedicated coprocessor hardware for a specific stream cipher. While the last mentioned team focused on a single algorithm, Tehrani et al. [TGMD20] focused on a few, but limited, LWC algorithms, including 64-bit block ciphers like GIFT-64-128 and Skinny-64-128. In their article, ZiBin Dai and XueRong Yu [DYSC07] aim to improve the speed of cryptography processing by utilizing a flexible, albeit limited, processor architecture. The authors suggest a specific method to enhance the efficiency of analyzed algorithms by introducing a new set of very long instruction word (VLIW) instructions. These instructions leverage paralleling processing elements for specific instructions and follow a conventional hardware/software design approach to enhance the performance and flexibility of cryptographic processing. However, their analysis is limited to older ciphers and does not cover lightweight ones. The authors focus on the VLIW and additional ISA as a single mechanism to improve performance, without extending the hardware architecture. This paper will elaborate further on this approach. In parallel to our conducted research and our basic short-version publication [GL23]<sup>2</sup>, Hao Cheng et al. [CGM<sup>+</sup>23] presented the design, implementation, and evaluation of Instruction

<sup>&</sup>lt;sup>2</sup>Best-paper award winner at IEEE NEWCAS conference

Set Extensions (ISEs) for nine of the ten LWC final round submissions, providing evidence for richer evaluation with respect to metrics related to implementation. The authors analyze the performance of these ISEs on a RISC-V processor and compare them to software implementations. The article focuses on the RISC-V additional ISA while keeping the processor architecture as 32-bit *native* processor, without hardware or conceptual architectural changes, more related to the realm of extendable and modular processors. Among other aspects and differences, we touch upon this significant aspect in this paper. Notably, the work from Cheng et al. focused on one ISE without the general goal of searching for an ISE which solves the min-max paradigm as we define it: "one minimal ISE which maximises its' performance impact on sets of algorithms jointly". Instead, their proposed ISE can be seen as a union of separate ISE per algorithm altogether.

#### 3.2 Our Contribution

The study provides a detailed description of Crisa-X, a classification of processor instruction extensions and tightly coupled acceleration logic for LWC algorithms. Accurately categorising these extensions is crucial in evaluating the trade-off between performance and area when integrating new instructions into a processor. In particular, this classification can aid in determining the optimal balance between hardware acceleration and software execution for a given processor architecture. We explore various ways to expand processor hardware to accommodate new instruction sets and discuss the necessary process architecture required to support these extensions. These enhancements are carefully designed to support a range of LWC algorithms simultaneously.

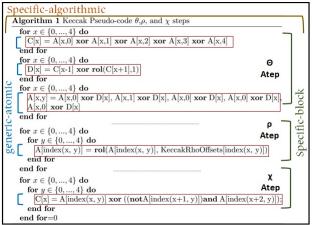

The Crisa-X ISA-extension instruction subsets include Generic-Atomic, Specific-Blocks, and Specific-Procedures categories, all of which greatly enhance the performance of NIST and CAESAR AEAD competitor algorithms. Generic-Atomic new instructions are a combination of bitwise operations designed for efficient computation with a small number of operands, allowing for the composition of a wide cryptographic permutation spectrum. The new instructions are executed efficiently within a single clock cycle. In contrast, Specific-Blocks are designed for extensive computation and serve as a foundational component for composing cryptographic permutation code. These new instructions exploit substantial memory- and instruction-level parallelism. To further enhance the acceleration of even larger blocks covering entire permutations, we introduce the Specific-Procedure instructions which establish the optimal subset to maximize acceleration. As significant computation is required for Specific-Blocks and Specific-Procedure, they are incorporated as tightly coupled acceleration logic within the processor pipeline. The research aimed to showcase our capability in solving a min-max problem by creating an extended ISA that can be used seamlessly by designers and cryptographers. The new set of instructions is designed to maximize impact across various cryptographic algorithms while minimizing costs and the number of required extended instructions.

Our main contributions are listed below:

- 1. The CrISA-X ISA new instructions stand out for their innovative computing capabilities, distinguishing between atomic, block, and procedure instructions, which cover a wide range of tradeoffs when it comes to latency performance and area utilization.

- 2. New instructions hardware implementation is carefully designed as single-cycle or complex multi-cycle specific operations to accommodate various architectural constraints and minimise the negative impact of the processor's critical paths and thus performance.

- 3. The proposed paper recommends the extension of the base processor hardware to facilitate the support of high levels of Instruction-Level Parallelism (ILP) and Memory-Level Parallelism (MLP) within the new Crisa-X ISA extension.

- 4. The CrISA-X classification also categorizes instructions into algorithm-agnostic and

- algorithm-specific types. For algorithm-agnostic applications, the CrISA-X ISA offers a versatile set of instructions suitable for all algorithms.

- 5. Depending on the required speedup, CrISA-X can be used for specific applications or a wide range of lightweight cryptography candidates while considering area budget.

- 6. This new instruction set incorporates Min-Max optimization to identify the computation level of ISA that minimizes processor area implementation, maximizes ISA versatility among various algorithms, and boosts performance, delivering optimal value. The search process within this extensive design space as elaborated.

- 7. The paper presents quantitative execution time analysis on a real synthesis modular processor design, offering insights into the actual performance of the new ISA set for various LWC algorithms.

- 8. The research introduces an efficient, automated methodology encompassing the identification of computation-heavy software blocks, ISA extension design for diverse classifications, simulation, validation, and the generation of synthesis processor RTL.

- 9. The CrISA-X ISA's toolchain support is versatile and compatible with various hardware platforms, including the Cadence Tensilica framework. Furthermore, it is designed to be freely shared within the academic community and released under an open-source license to promote transparency and collaboration.

# 3.3 Organisation

The paper is divided into several sections. The Introduction Section provides a background for this study and includes an in-depth analysis of related work in this domain. The list of our contributions is then presented. In the Methodology section, we describe CriSA-X in detail. We begin by describing our design flow and profiling, followed by the acceleration model, extendable processor, instruction extension, and the challenges we faced. In the Design section, we delve into the design considerations of CrISA-X for various LWC algorithms. Lastly, we introduce multiple implementation techniques and present the CrISA-X evaluation results on real hardware and simulation, and compare to all publicly available prior-art and available designs and public codes.

#### 3.4 Scope of our work

We have narrowed our focus to handle the extensive design space and engineering effort:

- 1. We are discussing a modular extensible processor with a base ISA that operates on 32-bit architecture. Our proposal for an additional new ISA encoding space ranges from 32-bit to 128-bit, which provides a wider set of ISAs and makes it more generally powerful. It is worth noting that the NIST call outlines a requirement to consider "8-bit, 16-bit, and 32-bit microcontroller architectures" [NIS22a], which is in line with our direction.

- 2. We focus solely on the AEAD encrypt and decrypt API, rather than both the AEAD and hash function API. The same kernel is used for both APIs.

- 3. We do not consider ISAP as the Ascon-p permutation used is already covered by other algorithms like Ascon.

- 4. In this work, we do not provide support in the base ISA or instruction extensions for implementing countermeasures against implementation attacks. This is left for continuous research.

# 4 Methodology

# 4.1 CrISA-X Design Flow

Designing an application-specific custom processor, along with custom instructions, is a challenging task for designers. They have to ensure that the resulting design is optimal

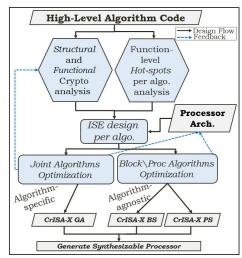

Figure: 2. High-Level design flow for CrISA-X instructions sets.

constantly. It is a time-consuming process that requires designers to evaluate numerous combinations of available parts that make up the processor. Achieving an optimal design is a difficult problem requiring much effort. Different design flows have been proposed to overcome such a difficult design choice. Figure 2 gives one such design flow, which outlines the process for designing CrISA-X instructions set for LWC algorithm. This design flow profiles a set of LWC application programs and associated data. Profiling is performed upon numerous processor configurations. Each configuration consists of the base processor with one or more coprocessors. For example, the configuration might be a base processor and a dual load-store unit. We gather extensive profiling analyzer data to identify "hotspot" functions across LWCs, together with structural and functional aspects of the code, particularly to the permutation implementation. Structural code analysis involves examining its physical structure or form without necessarily delving into its functionality. This analysis emphasizes the code organization, relationships between different program components, and the overall architecture of the algorithm. We identify the flow of control in the algorithm, including loops, conditionals, and branching. Additionally, we examine how data is organized and manipulated within the algorithm, including arrays, linked lists, trees, and more. This analysis helps us understand the code organization and flow and aid in identifying potential areas for optimization by the new ISA extension. Functional analysis, however, focuses on what the algorithm specifically does and how well it achieves its intended purpose. The profiling data allows us to learn where the program spent its time and which functions called which other functions while executing. This information can show which pieces of the program are slower than expected and might be candidates for rewriting to make LWC programs execute faster. It can also tell us which functions are being called more or less often than expected. The analysis of profiling data and cryptography's structural and functional elements holds significant importance in verifying code computations and their intensity. This analysis leads to developing new instructions to meet the increasing computational needs. Once the profiling has been performed on all these, a heuristic is used to select one of the configurations for further optimization. In the second step, we develop an ISE for each computation code. As the new instruction is tight to a processor architecture, we will examine both aspects during the implementation. Instruction extension is realized through a hardware implementation scripted in a specialized Hardware Description Language (HDL). The CrISA-X design is classified based on the encoding space and computation logic utilized to perform instructions. Other parameters, such as the number of operands used, input

Figure: 3. hardware/software co-design strategies (a) software only (b) loosely-couple (c) tightly coupled and (d) ISA extension.

and output data, and computation logic, are also considered. Furthermore, we endeavor to explore potential techniques for extending the modular processor to enable support for varying levels of logic in instructions. This extension will cater to instruction sets implementing low, mid, and high amounts of logic. The data output is designed to be ready in a single cycle for instructions categorized as low computation logic. However, for mid to high levels of computation logic, the implementation of computations spans multiple clock cycles, mostly two cycles. This is all made to minimize the impact on processor operation frequency. In the final step, we will analyze the tradeoffs and opportunities of using the new ISA extension among a larger set of LWCs. We will explore how multi-LWC algorithms can be created by building upon the single ISE designs and also search for opportunities to optimize joint algorithms. As a result of this optimization flow, each new instruction will be targeted for algorithm-specific or algorithm-agnostic use and algorithm C-code will update accordingly to use the new ISA extension. Every new instruction incorporated into an algorithm adheres to functional correctness. Also, each LWC application validates that the algorithmic behavior aligns with the original across various test patterns, which will be expounded upon later in this paper.

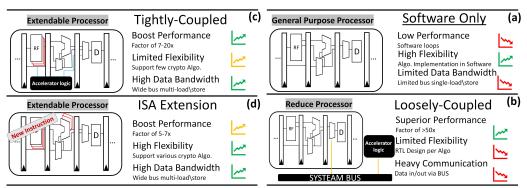

# 4.2 Selecting the Accelerator Models

To cope with reaching high-performance challenges, hardware/software co-design strategies are usually employed. For a given LWC algorithm, the goal is to find an optimal assignment of tasks between software running on reduced instruction set computer (RISC) processors and hardware implemented as accelerator logic. By splitting the tasks of an algorithm into hardware and software elements, high-speed and flexible implementations can be developed. Various options exist for accelerating cryptographic solutions based on embedded processor core [PMMB22, SZII11, Sea01]. These options differ in throughput, flexibility, range of solutions, and area cost. Refer to Figure 3 for illustrations of the main implementation options. Software implementation of cryptographic algorithms is clearly a simpler and easier approach. It does not require a specialized hardware block. It does not impact the die size and therefore does not raise system costs. This approach requires some code space in the instruction memory, making updating and maintaining the cryptographic code easy and affordable. The processor is designed to run algorithms with pipeline architecture efficiently, supporting conditional execution, function calls, and stack memory. It is also optimised for complex mathematical operations, including integer multiplications and floating-point calculations. However, processors may be less effective when executing cryptographic procedures involving many bitwise operations within a loop. This is because each bitwise operation can only be implemented as a single processor instruction in a single cycle [PS00]. Software-only implementations should be considered a last resort when

high-computation cryptography algorithms are required for low-latency applications on general-purpose processors.

A high throughput approach for accelerating cryptographic algorithms uses hardware logic, described in 3(b,c). Hardware logic accelerators can execute code in a few or single cycle and achieve significant speedup. There are two categories of accelerators: tightly and loosely coupled. In a loosely coupled (LC) implementation, an accelerator is positioned outside the processor core, and it operates independently like a co-processor. The LC accelerator logic works similarly to a hardware function call. It is designed to be out-of-core and communicate via a system bus. This prevents the logic from degrading the processor pipeline's performance. As a result, the accelerator logic blocks can be coarse-grained with complex data paths that accelerate a complete LWC kernel implementation. On the other hand, the BUS interface can take care of heavy communication back and forth from the processor to the accelerator logic. LC hardware implementation requires additional hardware space and power consumption for the overall cryptographic solution. This design mostly speeds up a specific cryptographic algorithm with limited configuration space. However, LC hardware implementation is not dependent on the operating system or runtime code. The operation frequency executed in out-of-core hardware can be different and faster than the core.

A tightly coupled (TC) approach involves adding accelerator logic fused into the core pipeline and adding new ISA instructions to use this logic appropriately. This approach adds hardware functional units that can operate in parallel with existing ones to expedite critical parts of an application kernel. Extending the processor hardware to support this additional logic can minimize data processing bootblack and boost the application performance. TC logic is part of the processor pipeline and interacts during pipeline stages. TC logic and the core pipeline can access the same resources, such as the register file, processor state, data memory, etc. New instructions designed as TC potentially stalled in case of data dependency constraints. TC includes special instructions in its ISA to manage operations, typically communicated to software through compilers or low-level libraries. A typical application case for TC is a sequence of bitwise operations that rely on different logic, like LWC permutation. Integrating TC accelerator logic can be challenging for hardware designers. Firstly, it can complicate the CPU design. Secondly, it may pose timing closure challenges since the TC logic is required to meet the same clock-frequency constraints as the processor. Finally, TC accelerators have limited flexibility in terms of portability across different LWC algorithms. From a system-level perspective, decoupling the LC accelerator from the processor provides greater flexibility than the TC model. With the LC accelerator running, the processor can perform other tasks or shut down to conserve energy. On the other hand, the TC model requires less effort from the compiler and toolchain since the LC extension is integrated into the pipeline and extended ISA.

A standard general-purpose processor can only perform single bit-wise logical operations on limited operands per cycle [PS00]. An alternative design strategy is to augment the core processor with custom 'light' instructions that fuse a few base ISAs together, as described in Fig. 3(d). Using those new custom instructions with extensible processors that have wide data and instruction interfaces will bring higher levels of data and instruction parallelism. These new instructions, which form a minimal set of additional instructions to the base ISA, are supported by the processor toolchain and can be executed in a single cycle compared to the same functional implementation with only basic ISA instructions. lightweight custom instruction can potentially improve computation block speed and reduce memory space without significantly impacting the processor timing paths and clock rate. Using the ISA extension method, we can implement LWC with fewer instructions as the new instructions are inline with kernel implementation, resulting in a significant boost in performance for long-latency calculations. As those new custom instructions fuse only a few operations together, they can potentially cater to a wide range of cryptographic

Figure: 4. Multidimensional Design Space for Customizable Processor

applications. Designing a lightweight extension ISA to support LWC achieves balance against high hardware costs, requiring expertise in application, instruction set design, and processor design.

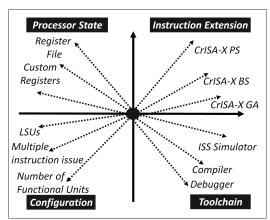

#### 4.3 Extensible Customizable Processors

The extensible customizable processor is rooted in the principles of classical Reduced Instruction Set Computing (RISC) architectures. It boasts the ability to be configured in numerous dimensions, as is illustrated in Figure 4.

Firstly, in terms of the basic design, several core architectural key elements can be incorporated to enhance the base processor, including functional units, instruction and data bus width, number of load-store units (LSUs), number of instruction fetch, etc. By carefully selecting and adapting the appropriate hardware block to the data and instruction processing needs, the processor architecture can be tailored to meet the specific requirements of LWC applications, resulting in improved algorithm execution times. Secondly, the base instruction set can be extended by user-defined custom instructions. Performance-critical code portions that require multiple instructions on a generic RISC architecture can be compressed into a single, user-defined instruction to obtain a significant speedup. Thirdly, The processor possesses an array of registers and states, including processor state, custom registers, and register files, that are expandable. By expanding these registers, we can boost the number of registers available or adapt them to varied data formats. This increases storage capacity for essential data, intermediate results, or control signals. With more register, the processor can access and manipulate crucial information more efficiently, reducing the requirement for frequent data transfers to external memory and elevating overall performance. Lastly, Implementing a new architecture necessitates a comprehensive update of the toolchain, including the instruction-set simulator, compiler, debugger, assembler, and all associated tools. By doing so, developers can create applications for the processor and evaluate their performance with greater efficiency and accuracy. It is imperative that this update is executed promptly to ensure the seamless integration of the new architecture into existing systems and to facilitate the development of optimized software for enhanced performance.

#### 4.4 Challenges with Instruction Extension

The augmentation of an existing processor's ISA with custom instructions extension has emerged as a popular approach for enhancing application execution speed. Nonetheless, designing a new instruction set architecture is a critical task requiring meticulous planning

and consideration. Developing an ISE poses several challenges that must be carefully addressed to ensure an efficient and effective design.

The first challenge in designing an extension is identifying the proper compute block to implement as new instructions. Cryptography tasks involve intensive mathematical computations using bitwise operations, memory access, and flow control, including data movement, manipulation, and boolean logic operations. Breaking down the function execution time is crucial in identifying software bottlenecks suitable for replacement by the new ISA extension acceleration. The design of the instruction extension must show measurable performance gains on the target workload. The instruction extension should focus on accelerating the application code's hottest and most frequently executed sections. This strategy is an application of Amdahl's law, which suggests that the useful effect of optimization is maximized by covering the dominant areas of the program code with acceleration. However, just replacing the group of base ISA sequences with new instructions doesn't guarantee a performance boost as there is a certain overhead for register load/transfer associated with a new instruction.

In order to guarantee that newly introduced instructions have a substantial impact on latency, **the second** challenge lies in identifying, within the *hottest* compute block, the specific components that should transfer the new instructions. This analysis should take into account a few parameters: (1) the input and output register amount and immediate values. this will impact the number of register file ports for input and output ultimately defining the bandwidth to and from the extension hardware. (2) registers width and datatype (3) points in logic data flow where there are no register mutual dependencies, and the instruction extension can be scheduled.

Designing a new ISA extension requires careful consideration of instruction encoding space as it is a limited resource, which makes instruction encoding the the third. As the encoding space is inherent in the processor bus width, the encoding scheme should be efficient, compact, and compatible with the existing encoding formats. While designing a new instruction, the challenge is to allocate the minimum space, considering the opcode, number of registers, immediate, and states, while achieving the maximum computation. This challenge will be addressed later in this paper by categorizing instruction according to encoder space and computing level. With a modular processor, we extended the instruction bus to be large, with more space for long instructions. Moreover, the VLIW option for partitioning the wide instructions into custom slots will create a multi-slot VLIW machine, each slot capable of executing one of a set of operations in parallel. We must carefully analyze and decide which instructions will get into groups based on the dependencies between instructions. There can be dependencies between instructions in a group, but they can cause pipeline hazards. This analysis should be per the LWC algorithm, and once we reach a solid optimal design, we should go one step further and tune which instructions will get into groups from joint algorithm aspects.

The power-performance-area (PPA) trade-off is a the **the forth** challenge. New instructions have direct implications for processor hardware. The processor area and timing are the most viable processor characteristics that get impacted and must be taken care of carefully. Heavy combinational logic embedded in the instruction logic impacts the processor area and can cause long-timing paths. for instance, new instructions may involve adding more function units that should work sequentially. Moreover, In the case of a few institutions running in parallel, there is a potential scenario in which more than one instruction needs to access the register file. Therefore, the register file design would have many ports, potentially muxing together, creating a more complicated access path, being prominent in the area, and possibly bringing timing constraints. Instruction extension design must also consider the cost and power implications of adding new instructions to the processor. New instructions can increase the processor's size and complexity, leading to higher costs and power consumption and decreasing the max processor frequency. A

well-designed ISE can result in a lower footprint in the hardware area, i.e., gate-gate.

# 4.5 Profiling

Identifying and adding instruction extensions to existing base processors has been extensively studied. A significant body of literature has been published on this subject over the years [CMS07, CZM03, KR06, YM04, CHKP98]. The typical approach involves starting from the application code, identifying a large set of ideal ISE candidates from a compiler intermediate or from generated convex sub-graphs from the data flow graph (DFG), and then searching for the optimized ISE. Although, those methods satisfy the processor I/O constraints, the outcome is limited for specific processor architecture. It does not consider the various options to extend the processor hardware for DLP and ILP to gain more speedup for computation block across more than one algorithm. Our philosophy is different, and we used a profiling analyzer based on the GNU gprof [FS88] to identify "hotspot" functions across a set of LWCs. The "hotspot" function consumes a substantial amount of the execution time of the specific algorithm. The profiling step gathers data about the application instructions executed with "hotspot" functions from the actual execution of the program. Instruction Set Simulator collects profile data from the target application in a non-intrusive manner so that it does not affect the actual functioning of the original code. The profiling tool records the execution of every instruction in a cycle accurate manner. We use different types of analysis outputs to understand our program's performance. The flat profile shows how many times each function was called and how many cycles it used. This information helps us identify the functions that require the most computation. The call graph displays the amount of time taken by a function and its associated functions. By analyzing this information, we can identify functions and the function assembly code, that may not take much time but trigger other functions that consume substantial amounts of time. Finally, we use line-by-line profiling, assigning histogram samples to individual assembly lines of source code instead of functions.

Profiling data guides the block computation selection of which translate to CrISA-x instructions set. The profiling step of the process is performed using a cycle-accurate instruction set simulator (CA-ISS) that supports both the entire base ISA and the introduced new extended CrISA-x instructions. The CA-ISS model simulates the processor at an abstraction level between the RTL and the functional model. It presents the architectural details necessary for the processor dimension to evaluate its performance capabilities in advance. A CA-ISS runs on a host machine to mimic the functional behaviors of instructions running on target hardware. CA-ISS allows the estimate of the execution time of software in a cycle accurate way and validates a system even when its target hardware does not yet exist or is not available. A CA-ISS reflects a target hardware logic and conforms to the cycle-by-cycle behavior of the target system. It can produce the same number of cycles as the actual execution on the target hardware. We used the execution statistics gathered by the profiling tool, combined with instruction timing values, like cycles required to execute each instruction, to give an accurate number of cycles required to execute the application on the base ISA and with CrISA-x instruction. The speedup of the enhanced ISA version relative to the base ISA version can be computed and compared fast. The profiling tool determines how many cycles are required to emulate each instruction executed from the full ISA, which is not supported by the base ISA. This is calculated by counting the number of base instructions executed by software modules used to emulate these instructions and scaling the results according to the number of clock cycles that are required to execute each base instruction executed.

#### 4.5.1 CrISA-X illustration

An illustrative example will be presented in this section to provide a comprehensive understanding of the CrISA-X methodology. Furthermore, we will show the concept of issuing multiple instructions, including CrISA-X, on the same cycle. Later in this paper, we will delve deeper into these topics, examining them in greater details.

To illustrate these, consider the ASCON permutation described in listing 1, where profiling numbers (mark as (xK)) indicate that significant application's execution time is spent computing the c-code statement as part of permutation flow.

Listing 1: Basline c-code Ascon permutation

The provided C code explains how the permutation works in both linear (lines 1-4) and nonlinear parts. For example, in the linear part (e.g., lines 1 and 2) section, two data input registers, one odd (o) and one even (e), are XORed, which requires two base instructions, not counting the instructions required for loading and storing the data. Later in the code, in the nonlinear section, an intermediate value goes through a bitwise NOT operation, and then a bitwise AND operation is performed. The result is then XORed to obtain the final value, which takes three base instructions. In line 6, an instruction involves rotating a 32-bit input by performing a circular shift, followed by XORing the result to obtain the final value. This operation comprises two basic instructions.

Listing 2: Crisa-X code Ascon permutation

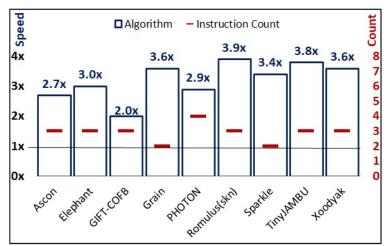

As described in listing 2, these c-code and corresponded assembly instruction can be fused into **three** different single-cycle fused instructions called XOR2, XORNOTAND, and XOROT. Each instruction uses one or two input operands from the processor register file to compute the output value and save it back to the register file. The semantics of those instructions and others will be described later. The software toolchain updates as-well and recognizes the new instructions in addition to the processor base ISA. Fused instructions, as described in listing 2, are significantly cheaper in area and have a limited access port for the register file because they operate on restricted data sets. A computation that previously took seven assembly bitwise operations, each taking seven cycles per iteration on a base processor, now only requires three cycles, resulting in nearly a 3x performance increase. This kind of instruction will be defined later on in this paper as Crisa-X Generic Atomic.

Instructions extensions that involve more input and output operands, and therefore implement more involved computation can be designed with logic that spans multiple clock cycles. Such instructions, defined later in this paper as Crisa-X *Block Specific* and *Procedure Specific* can be fully pipelined and can be issued back-to-back or in an iterative manner. Fully pipelined instructions achieve higher performance because they can be

issued back-to-back, but they may also require extra implementation hardware to store intermediate results in the instruction pipeline.

Creating instruction extensions for customized processors goes beyond the fusion of several operations into a single instruction. We can improve instruction-level parallelism (ILP) by bundling multiple instructions into a single long instruction word (LIW) and executing them simultaneously in parallel. In VLIW, the compiler explicitly schedules multiple independent instructions into a single, long instruction word, which is then issued to the processor, executing all instructions in parallel. Different types of instructions can be used, including base instructions and dedicated CrISA-X instruction, which can be freely intermixed to optimize performance. The instructions are divided into slots. Each slot represents a group of instructions that can be executed in parallel within a single clock cycle. Slots are not equally sized. Any combination of the operations allowed in each slot as far as the encoding space allowed. With multiple instructions bundled into a single slot, the processor only needs to fetch and decode one instruction word per cycle. This simplifies the instruction fetch and decoding stages, reducing the complexity and overhead of these stages in the processor's pipeline. Slots allow the processor to efficiently utilize its available resources, such as functional units and registers

Consider the Ascon permutation example. The inner loop performs the actual computation using three-fused instructions. It also utilizes two L32I load instructions and one S32I store instruction to move the data as needed<sup>3</sup>. Additionally, listing 3 describe the ILP way to accelerate this code. In this example we are using a 64-bit instruction format with one slot for the load and store instructions two slot for the computation instructions.

Listing 3: Ascon permutation slot setting

```

format flix3 64 {slot0, slot1, slot2}

slot_opcodes slot0 {LD_INST,ST_INST}

slot_opcodes slot1 {LD_INST, XOR2}

slot_opcodes slot2 {XOR2,XORNOTAND,XOROT}

```

The first declaration creates a 64-bit instruction and defines an instruction format with three opcode slots. The last three lines of code list base ISA instructions to be available in each opcode slot defined for this processor slot configuration. Note that all the instructions specified are predefined, some of them are core processor instructions, and others are CrISA-X. For this example, the compiler can compile the source code using slot extension definitions without any changes to the generated C/C++ program. The generated assembly code for this processor implementation is described in listing 4:

Listing 4: Ascon permutation assembly VLIW look

```

1 loop:

2 {$LD_INST;LD_INST;XOR2}

3 {$ST_INST;LD_INST;XORNOTAND}

4 {$ST_INST;XOR2; XOROT}

```

A computation that requires fourteen cycles (nine cycles for operation and 5 cycles for load-store) per iteration/data input on a base processor, with multi-issue and extended ISA only requires three cycles per iteration, resulting in nearly a 5x performance increase. In the context of supporting multiple algorithms and achieving pareto-optimality, it is necessary to establish an instruction slot format that ensures no algorithm can be improved without negatively affecting another algorithm. This is accomplished by striking a balance between the various algorithms, such that we add ISEs for each algorithm so that it can

<sup>&</sup>lt;sup>3</sup>Noted that the term "32" in this context pertains to operands with a bit length of 32, while "I" denotes an immediate value integrated directly into the instruction.

Figure: 5. CrISA-X Classification together with Processor Extensions. Previous work (red) described in Table 2

perform well on its own, and we increase as little as possible the complexity of these new ISEs so that they can be shared as much as possible between algorithms; clearly, without increasing cost and area significantly.

# 5 Design

In designing CrISA-X for performance-acceleration of LWC code, we have adopted a two-fold approach comprising the design of an instruction extension and processor extension. This approach optimizes LWC code performance by leveraging the ISA extension's capabilities and the extended RISC processor. By doing so, we can extend a group of custom hardware resources to support a new instruction set. Adopting a new instruction set and removing constraints on processor architecture minimize the processor area and maximize the utility of ISE designs. The relationship between software and hardware processors is illustrated in Figure 5. In the case of an extendable processor, CrISA-X instructions are defined and formatted as part of implementing the software layer for LWC. The base ISA is the sole means of interaction between applications and the underlying hardware at the lower layer. The CrISA-X Extended ISA specifies additional instruction using function unit extensions and registers throughout the processor's extended ILP and DLP hardware.

## 5.1 Extending Processor Architecture

The processor architecture can be extended in several dimensions: (1) The scalar Register File has been extended to support multiple input and output operands with multi-read and write ports. (2) The width of the processor's data and instruction bus has been extended to allow for simultaneous transfer of instructions and operands, reducing memory accesses. (3) The processor fetch and execution units have been designed to execute multiple instructions in parallel by packing them into a single long instruction word. This parallel execution allows for improved performance by exploiting ILP. (4) Extending the processor with additional load/store hardware to allow multiple memory operations to be executed in parallel. (5) Additional constant, state, and array registers have been added to the processor's register space. These single-cycle access registers are built along the processor pipeline to provide dedicated or temporary storage that can be shared and used between new instruction sets. (6) Instruction extension includes fused and SIMD operations. The first creates new instructions composed of several simple bitwise operations

Figure: 6. (a) CrISA-X trade-offs Power-Performance-Area(PPA) vs Number of operands, Functional-Units (FUs) and amount of computation (b) CrISA-X categories

and the second designs instructions that simultaneously perform operations on multiple data elements.

# 5.2 Extending Processor Instruction Set

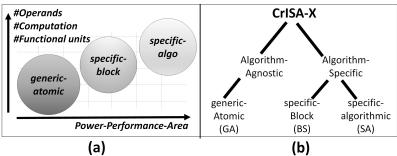

Various implementation styles are available when designing an accelerator to support cryptographic algorithms on a general-purpose processor. These techniques can be algorithm-agnostic or algorithm-specific and use hardware, software, or a hybrid approach using Extended ISA. The approaches of Extended ISA can be categorized based on the number of operands, amount of computation, and instruction encoding space. These are dubbed specific-atomic, specific-block, or specific-algorithmic ISA as describe in Figure 6.

The **generic-atomic** (GA) approach is an instruction extension that encapsulates several bitwise operations happening in series, which are not available as part of the base ISA. CrISA-X GA usually have two to four operands, with part of them serving as the destination. The instruction encoding is kept short. These instructions are algorithm-agnostic, allowing them to be applied to any type of algorithm. This versatility makes them suitable for implementing a vast spectrum of LWC implementation. Their re-usability across different contexts and applicability to a wide range of cryptographic algorithms ensures they can balance performance and flexibility in general cryptographic implementations.

The **specific-block** (SB) family refers to an instruction extension that encapsulates multiple bitwise operations and accomplishes large computational tasks that might executed within a multi-cycle. CrISA-X SB instructions usually involve a substantial number of operands, typically ranging from four to eight, with one or more serving as the destination. The instructions use few parallel execution units to support narrower permutation building blocks that require a significant amount of computation.

The *generic-atomic*, GA, and *specific-block* approaches prioritize certain operations within the scope of individual permutations. The **specific-algorithmic** (SA) approach, on the other hand, encompasses a comprehensive sequence of operations that span across the entire permutation block as an interdependent single unit.

The specific-algorithmic is an instruction extension designed as tightly coupled acceleration logic that spans over more than a single cycle. The logic represents specific tasks, such as Ascon or Keccak permutation, and targets extensive computation. Instructions from this family involve multiple operands, often more than eight, and one or more serve as the destination. The length of instruction encoding is wide. The CrISA-X SA has been designed to avoid register spills to stack memory, i.e., temporary load and store operations during the permutation round. The extensive computation behind a specific algorithmic instruction allows for significant performance improvement when executing cryptographic LWC. However, the hardware implementation necessitates an increased gate count and impacts the maximum frequency of the processor pipeline. To minimize the impact on the critical path, we divide the specific algorithmic logic computation into two cycles and

Figure: 7. Ascon's Permutation steps

retime the signals as necessary.

Readers which are more focused on understanding bottom-lines and conclusions, and less interested in the deep technical details per each algorithm, can continue reading from Section 6.

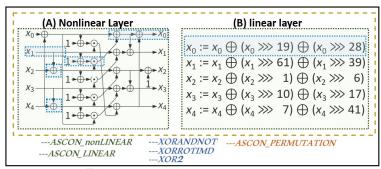

#### 5.3 ASCON

The Ascon submission presents a detailed analysis of several algorithms, including Ascon-128, Ascon-128a, Ascon-80pq, Ascon-Hash, and Ascon-Hasha, as reported in the work of Dobraunig et al [DEM<sup>+</sup>19]. However, the primary focus of the submission is on the Ascon-128 algorithm and its kernel. This kernel is composed of the pa and pb kernel permutations, where "p" denotes a single permutation, and "a" and "b" represent the number of rounds. The Ascon permutation, denoted as "p", comprises three layers: Round constant addition, Substitution layer, and Linear layer. This permutation operates on a 320-bit state, divided into five 64-bit words  $\chi 0$ ,  $\chi 1$ ,  $\chi 2$ ,  $\chi 3$ , and  $\chi 4$ . In the round constant addition layer,  $\chi 2$  input is XORed to the round-specific constant. The substitution layer is typically implemented using logical ANDs, XORs, and NOTs, while the linear layer employs shift left and XOR operations.

CrISA-X description: To demonstrate the CrISA-X instruction set, the Ascon-128 algorithm is used in a bit-interleaved manner on a 32-bit processor. Each 64-bit word of the state is divided into two 32-bit words. One word contains the bits at even positions, and the other word contains the bits at odd positions. This representation can exploit the 32-bit register extension without paying latency overhead for accessing a 64-bit register file. However, this comes at the expense of conversions between the bit-interleaved representation and 64-bit representation whenever data is injected into or extracted from the state. CrISA-X hides this latency as part of the instruction logic as it includes bit extraction from the state as a pre-operation.

The bitwise logic for the non-linear and linear layers is illustrated in Figure 7. These layers involve logical operations performed on 64-bit words, which can be split into two operations on 32-bit chunks. The substitution box requires extensive base instructions, split between 44 XORs, 12 NOTs, and 10 ANDs, 19 shifts, and 19 ORs, spread between even and odd parts. In total, there are about 104 native instructions per round. Depending on the amount of computation it encapsulates, the various uses of the CrISA-X instruction are represented by different colors, as shown in Figure 7. It takes 16 instructions to implement the generic-atomic in the linear layer, while the non-linear layer requires 14 CrISA-x instructions, resulting in a total of about 30 CrISA-X instructions. The permutation layer can significantly speed up the process by a factor of 5x. Figure 8 describes the generic-atomic semantic use to speed up Ascon permutation. Immediate values can be used to specify rotation amounts. When implementing the S-box with the specific-block approach, only the new 8 instructions' are needed. The linear layer requires the new 10 instructions'

```

XORNOTAND at, as1, as2

at \Leftarrow at \text{ xor (( not } as1) \text{ and } as2)

XORROTIMD at, as, imm

at \Leftarrow at \text{ xor } (at >> imm) \text{ or } (at >> 32 - imm)

XOR2IMD at1, at2, imm1, imm2

at1 \Leftarrow at1 \text{ xor } imm1

at2 \Leftarrow at2 \text{ xor } imm2

XOR2 at1, as1, at2, as2

at1 \Leftarrow at1 \text{ xor } as1

at2 \Leftarrow at2 \text{ xor } as2

```

Figure: 8. CrISA-X Generic Atomic instruction for Ascon permutation

Figure: 9. CrISA-X Block-Specific for Ascon Linear layer

$\textbf{Figure: 10.} \ \textit{CrISA-X Block-Specific for Ascon Nonlinear layer}$

when using the wide instruction bus approach. With this, the permutation layer can achieve a speed-up of up to 8 times faster. while implementing with *specific-procedure* brings 10x factor. Figures 9, 10 describe the appropriate semantic for block level.

#### 5.4 Elephant

The mode of Elephant is a nonce-based encrypt-then-MAC construction, where encryption is performed using counter mode and message authentication using a variant of the protected counter sum MAC function. The Elephant submission specifies a few AEAD

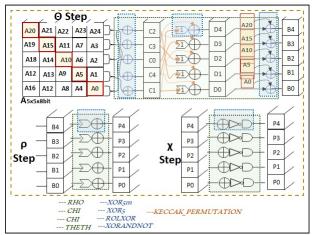

algorithms, Dumbo, Jumbo, and Delirium [DEM<sup>+</sup>19]. To focus we choose one and specifically concentrate on Delirium: namely Delirium = Elephant-Keccak-f[200].

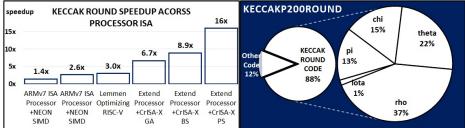

The delirium permutation was selected because the keccak permutation is widely used in other lightweight algorithms. The Keccak-f permutation is the fundamental building block for SHA3, and for two candidates in the CAESAR competition, namely KEYAK and KETJE [BDP+14, BDPA15, Dwo15, RS16]. The permutation function is computed using 25 Keccak states, marked as A0 to A24. Each state is 8 bytes and the iteration is performed over a set of 8 rounds. The state data can be saved using extended register files, resulting in fewer data movements than only exploiting register files in the baseline core. In brief, five keccak steps are defined by five operators symbolized by  $\theta, \rho, \Pi, \chi, \iota.$   $\theta$ , The most extensive ones are illustrated in Figure 11.  $\theta$  step requires XOR between five states, then rotating left by a factor of one to get Di states. The last step is Di states XORs with Ai states.  $\rho$  step is for left rotate all lanes in the state by a fixed offset. For efficient implementation of the  $\rho$  step, left rotation by the *Keccak* constant tables are saved as the hardwired processor state. In the  $\Pi$  step, all lanes in the state are transposed in a fixed pattern. This step can be done using only MOV instruction. Next, is  $\chi$ , where each bit of the lane is non-linearly combined with the bits of nearby lanes using AND, XOR, and NOT instructions. Last is  $\iota$ : a simple XOR of constants into a single lane. An in-depth explanation of the keccak permutation can be found in the reference [BDPVA09]. The state of a 5x5x8bit keccak can be viewed as w-slices of 25 bits each or as five planes with five lanes of 8 bits each. Our research employs a layered design that groups four states into a single 32-bit input. The CrISA-X instruction logic effectively hides the latency penalty by handling data separation back to an 8-bit representation as part of the instruction. All the steps involved in the keccak algorithm, except for  $\Pi$  and  $\iota$ , can be efficiently performed using the CrISA-X instruction from various categories. The  $\Pi$  and  $\iota$  steps mainly involve moving data from one register to another and do not have a significant impact on latency.

CrISA-X description: To showcase the CrISA-X instruction set, we decided to store the keccak in the extended register file. We wanted to work only with full 32-bit variables instead of 8-bit variables. Thus, we replaced all byte variables with uint32 variables, which resulted in a state representation that consisted of an array of seven 32-bit words. The Keccak permutation steps are illustrated in Figure 11. Each category of CrISA-X instructions is represented by a different color. For the generic-atomic instruction set, we use XOR5 and XOR5m, the last one involving immediate value as inputs. These institutions perform XOR operation between five operands or immediate and produce the result in a single cycle. In addition, two new fusion instructions have been designed: ROLXOR, which brings rotate-left and XOR together, and XORANDNOT, which fuses XOR with the result of NOT-AND operations. Figure 12 presents the pseudo-code for Keccak and demonstrates the use of specific-block and specific-procedure instead of original operations. The instruction set for the specific block implements the full  $\theta$ ,  $\rho$ , and  $\chi$  keccak steps in a single instruction. 'Block' operation approach is possible for custom processor hardware where the state can be stored in a custom register file. Instruction logic can efficiently read the state in a lane-wise or fashion, and operate, depending on the keccak step. The keccak state is composed of 200 bits, which can be arranged in seven 32-registers. This allows for the creation of a hardware logic that can perform all permutations in one instruction, known as a specific procedure. The input and output for this instruction will be seven 32 registers from the extended register file. The logic of the instruction includes five Keccak operators -  $\theta$ ,  $\rho$ ,  $\Pi$ ,  $\chi$ ,  $\iota$ .  $\theta$  executed back-to-back.

#### 5.5 GIFT-COFB

GIFT-128 is a member of the GIFT block cipher family. It uses a substitution-permutation network (SPN) with the key length and block size set to 128 bits. The algorithm and its implementation are described in reference [BCI+19,BPP+17,MSA22]. The function

**Figure: 11.** keccak permutation  $\theta$ ,  $\rho$ , and  $\chi$  steps

Figure: 12. Keccak pseudo code along with CrISA-X classification

Figure: 13. Quintuple steps description

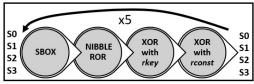

giftb128() is the most cycle-intensive function, and it consumes 90% of all the LWC reference code and implements a 40-round block cipher. Input is a 128-bit cipher state expressed as four 32-bit slices S0, S1, S2, and S3. The round function consists of quintuple steps repeated eight times. Each quintuple step is a group of operations that happen in serial and are repeated five times. the steps are: SBOX, Nibble\byte\half-word rotate right, then result in XOR with round-key and last with round-constant, describe in Figure 13.

**CrISA-X** description: The *GIFT-128* cipher uses a 32-bit register nativity. Thus, the CrISA-X instruction is designed to take advantage of this and focuses on fusing bitwise operations into a single instruction that can be executed in a single cycle. Three new fusion instructions have been developed for the *Generic Atomic* set: XORAND, ROTOR, and XORSHFTAND. Instructions semantics are described in Figure 14. They are used as

Figure: 14. CrISA-X Generic Atomic instruction for GIFT-COFB permutation

building instructions to speed-up core computation. With the *Specific-Block* set, we design interactions that take as input the four S0, S1, S2, and S3 and compute the full SBOX. The same is performed for other instructions: ROTOR, ROTXOR, and SWAPMOVE. For the *Specific-Algorithm*, we design a single interaction that calculates QUINTUPLE round in a single instruction.

#### 5.6 Grain-128AEADv2

Grain-128AEADv2 is an authenticated encryption algorithm with support for associated data. we logically divide the cipher into two phases. The first phase is the loading phase, in which the shift registers are loaded and initialized with the key and the nonce. Second, the cipher enters the running phase, in which pre-output is generated both for encryption and authentication. A pre-output generator is constructed using a linear feedback shift register (LFSR), and a non-linear feedback shift register (NFSR), which are 128 bits each, and generates a stream of pseudo-random bits used for encryption and the authentication tag. The authentication phase consists of a shift register and an accumulator. The algorithm performs several functions, but the keystream generation, authentication, and loading phases require the most cycles. In these phases, the system works with 32-bit words and uses various bitwise operations such as shifts, ANDs, and XORs to calculate feedback bits for LFSR and NFSR and generate the new key stream.

CrISA-X description: We created fusion instructions composing multiple operations into one to speed up such operations. For the Generic-Atomic set, we use the ROTXOR instruction, which its semantics is describes in Figure 16. This flexible instruction can take three 32-bit operands as input, one operand as output, and two immediate values. By shifting the bits individually, we can extract a 32-bit word from a 64-bit word in many different ways. The authentication mechanism in Grain-128AEADv2 is based on a universal hash function, introduced in [WC81]. For hashing, the message is multiplied by a Toeplitz matrix where the Toeplitz matrix multiplication is implemented using XOR the shift register with the accumulator for each single bit in the byte that we are authenticating and shift in the keystream byte that has been retrieved before, for that we use Generic-Atomic ROTXOR, SHIFTLXOR and XORAND operations. Extending the processor data bus to 128 bits, we can load and save all state data back to memory with a Spcific-Block instruction called LOAD128B and STORE128B. After loading the data, it can be divided into four 32-bit variables: S0, S1, S2, and S3. These variables are saved on the processor's extended register file and available for both CrISA-X and base instructions. The algorithm extracts a 32-bit word from a 64-bit register through independent registers, so we can fuse them in a single instruction. We utilize this data group and create Specific-Block instructions calculating the BLOCKROTXOR as illustrated in Figure 15. For Specific-Algorithmic, we use the same processor extension to design a single instruction for the entire core computation of GRAIN128\_NEXT\_KEYSTREAM.

Figure: 15. GRAIN128 extract a 32-bit word from a 64-bit register with Specific-Block

```

ROTXOR at, as1, as2, imm1, imm2

at \Leftarrow as1 \text{ xor}(as1 \gt\gt imm1) \text{xor}(as2 \lt\lt imm2)

```

Figure: 16. CrISA-X Generic Atomic instruction for Grain128 core

```

XOROR2(XORAND2) at1, at2, as1, as2, imm1, \ imm2 at1 \Leftarrow at1 \ \text{xor} \ as1, \ at2 \Leftarrow at2 \ \text{or(and)} \ as2

```

Figure: 17. CrISA-X Generic Atomic instruction for PHOTON-Beetle core

#### 5.7 PHOTON-Beetle

The PHOTON-Beetle is an authenticated encryption and hash family, that uses a sponge-based mode Beetle with the PHOTON256 being the underlying permutation [BCD<sup>+</sup>19]. We focus on the primary algorithm PHOTON-Beetle-AEAD[128] bit sliced version. The PHOTON256 permutation operates on an internal state of 256 bits. Bit-slicing code slices the 256-bit data into an 8x32 words array, organized in 8 rows. The permutation is composed of 12 rounds, each applying 4 round functions: these are AddConstant, SubCells, ShiftRows, and MixColumnsSerial. SubCells applies a 4-bit S-Box to each of the 64 4-bit cells. ShiftRows rotates the position of the cells in each of the rows, and MixColumnSerial linearly mixes all the columns independently using serial matrix multiplication.

CrISA-X description: The AddConstant step performs the XOR operation on each word out of eight with the correct constant. To make this operation faster, we utilize the Generic-Atomic XOR2 instruction to double the throughput. Additionally, we save the round constant as a hard wire table. This helps to minimize the new instruction encoding as we only use an index reference to the constant table. To fully utilize the capabilities of the 32-bit processor and its extensions, we used the bit-slicing code for PHOTON256, especially this can be seen for the SubCells step. The basic concept of bit slicing involves converting the code into a sequence of logical operations such as AND, XOR, OR, and NOT, which can be executed on a standard-processor ISA [SOM]. For the Generic-Atomic instruction set, we have combined and optimized several operations into a single instruction, such as XOR2, XOROR, and XORAND as described in Figure 17, that executes as a single cycle. During the ShiftRows steps, we use the ROTOR instruction that rotates left by immediate positions for each row per BYTE. As CrISA-X instructions use 32-bit inputs\output operands, ROTOR instruction operates on four bytes in parallel, quad the throughput. The data is separated internally as part of the instruction to hide any additional latency penalty. PHOTON 256-bit state can be divided into two groups, with each group of 128 bits mapped to four 32-bit registers. Since the input states are independent and the SBOX non-linear operation is performed per 4-bits, we build a parallel

computation block to produce a 4-bit x 32 non-linearity operation in a single cycle. We utilize this data group and create *Specific-Block* SBOX instruction to accomplish this. The same concept was implemented for *ShiftRows* step where we rotate 16 bytes in parallel. For *Specific-Algorithmic*, we utilize a processor extension to create a single instruction that carries out the core computation of SBOX for the entire 256-bit input. *Specific-Algorithmic* PHOTON\_PERMUTATION uses 8x32bit register as inputs\output. This greatly impacts the register file as we significantly increase the number of ports. combining *Specific-Algorithmic* instruction with wide data load and store instructions (referenced as LOAD128 and STORE128), we achieve a significant speedup in the permutation.

## 5.8 Romulus

The Romulus submission describes the AEAD algorithms Romulus-N/M/T and the hash function algorithm Romulus-H. The computational complexity and latency of the kernel in Skinny-128-384-plus tweakable block cipher is high hence our focus was on it. This kernel operates on an internal state of 128 bits, representing a 4x4 matrix of bytes, similar to AES. The round function is composed of five operations in the following order: SubCells, AddConstants (AC), AddRoundTweakey (ART), ShiftRows (SR), and MixColumns (MC). SubCells applies an 8-bit S-box. The AddConstants operation XORs some round-dependent constants to the first column of the state. AddRoundTweakey extracts eight bytes from the tweakey state and XORs them to the state, whereby the bytes are permuted and updated with simple LFSRs. ShiftRows rotates the bytes of the state row-wise to the right by 0, 1, 2, and 3 positions, similar to the *ShiftRows* Right-rotate line i by i positions. Finally, MixColumns multiplies each byte-column of the state multiplied by a binary matrix. The skinny opt32 implementation relies on fix-slicing with QUADRUPLE ROUND routine [AP20]. Fix-slicing mainly consists of fixing the bits within a register (or slice) never to move and adjusting the other slices accordingly so that the proper bits are involved in the SubBytes operation. This implementation doesn't compute the ShiftRows operation. Some masks and shifts are applied during the MixColumns operation so that the proper bits are XORed together. Furthermore, the row permutation within MixColumns and the bit permutation at the end of the Sbox is omitted. The rows are synchronized with the classical after only four rounds.

CrISA-X description: The input for the *skinny128* core computation is a 128-bit state split into four 32-bit registers representing a 128-bit state. Core executing QUADRUPLE ROUND routine ten times. QUADRUPLE ROUND includes XOR and OR operation on each 32-bit state register, swap bit and mask, and add round key. We use a *Generic-Atomic* XORNOTOR instruction that fused the bitwise operation to a single instruction. We use *Generic-Atomic* XORSHFTAND instruction to swap the bits with masks. *Generic-Atomic* XOR2 instruction helps to double the throughput of adding round-key constant as this is done for each 32-bit state. Using the *Specific-Block* approach, we have implemented the QUADRUPLEROUND routine as a new CrISA-X instruction. This instruction takes the 128-bit state matrix split into four 32-bit words (quads) and the relevant tweak keys (TK1, TK2, TK3) and offsets. It implements this part of the encryption for a single block logic as a series of XORNOTOR, SWAPMOVE, followed by XOR2. The instruction we implement for *Specific-Procedure* is the new CrISA-X instruction, which includes the computation of all SKINNY128\_384\_PLUS and involves ten QUADRUPLE ROUND calls.

#### 5.9 Sparkle

Sparkle is a group of cryptographic permutations, each of which operates on a different block size - 256, 384, or 512 bits [BBdS<sup>+</sup>19]. The principal member of Schwaemm is Schwaemm256-128, which takes a 256-bit nonce and a 128-bit key as input and produces

```

SWAPMOVE at1, at2, as1, as2

tempreg \Leftarrow (at2 \operatorname{xor}(at1 \gt{as2})) \operatorname{and} as1

at1 \Leftarrow at1 \operatorname{xor}(tempreg \lessdot (as2))

at2 \Leftarrow at2 \operatorname{xor}(tempreg)

XORNOTOR at1, as1, as2

at1 \Leftarrow at1 \operatorname{xor}(\operatorname{not}(as1 \operatorname{or} as2))

```

Figure: 18. CrISA-X Generic Atomic instruction for Romulus

```

(A) Nonlinear Layer

(B) linear laver

x + (y \gg 31) | (y << 1)

y \oplus (x \gg 24) \mid (x \ll 8)

x \oplus c

\bigoplus y_i,

y \oplus (x \gg 17) \mid (x <<5)

-x_i \oplus \ell(t_u), \forall i \in \{0, ..., w-1\}

v_i \leftarrow y_i \oplus \ell(t_x), \ \forall i \in \{0, ..., w-1\}

\ell(x) = (x \ll 16) \oplus (x \& 0xffff)

SHIFTLXOR