# Randomness Generation for Secure Hardware Masking – Unrolled Trivium to the Rescue

Gaëtan Cassiers<sup>a,1</sup>, <sup>1</sup>, Loïc Masure<sup>2</sup>, Charles Momin<sup>1</sup>, Thorben Moos<sup>1</sup>, Amir Moradi<sup>3</sup>, and François-Xavier Standaert<sup>1</sup>, <sup>1</sup>

<sup>1</sup> Crypto Group, ICTEAM Institute, UCLouvain, Louvain-la-Neuve, Belgium <sup>2</sup> Université de Montpellier, LIRMM, CNRS, Montpellier, France

<sup>3</sup> TU Darmstadt, Darmstadt, Germany

**Abstract.** Masking is a prominent strategy to protect cryptographic implementations against side-channel analysis. Its popularity arises from the exponential security gains that can be achieved for (approximately) quadratic resource utilization. Many variants of the countermeasure tailored for different optimization goals have been proposed. The common denominator among all of them is the implicit demand for robust and high entropy randomness. Simply assuming that uniformly distributed random bits are available, without taking the cost of their generation into account, leads to a poor understanding of the efficiency vs. security tradeoff of masked implementations. This is especially relevant in case of hardware masking schemes which are known to consume large amounts of random bits per cycle due to parallelism. Currently, there seems to be no consensus on how to most efficiently derive many pseudo-random bits per clock cycle from an initial seed and with properties suitable for masked hardware implementations. In this work, we evaluate a number of building blocks for this purpose and find that hardware-oriented stream ciphers like Trivium and its reduced-security variant Bivium B outperform most competitors when implemented in an *unrolled* fashion. Unrolled implementations of these primitives enable the flexible generation of many bits per cycle, which is crucial for satisfying the large randomness demands of state-of-the-art masking schemes. According to our analysis, only Linear Feedback Shift Registers (LFSRs), when also unrolled, are capable of producing long non-repetitive sequences of random-looking bits at a higher rate per cycle for the same or lower cost as Trivium and Bivium B. Yet, these instances do not provide black-box security as they generate only linear outputs. We experimentally demonstrate that using multiple output bits from an LFSR in the same masked implementation can violate probing security and even lead to harmful randomness cancellations. Circumventing these problems, and enabling an independent analysis of randomness generation and masking, requires the use of cryptographically stronger primitives like stream ciphers. As a result of our studies, we provide an evidencebased estimate for the cost of securely generating n fresh random bits per cycle. Depending on the desired level of black-box security and operating frequency, this cost can be as low as 20n to 30n ASIC gate equivalents (GE) or 3n to 4n FPGA look-up tables (LUTs), where n is the number of random bits required. Our results demonstrate that the cost per bit is (sometimes significantly) lower than estimated in previous works, incentivizing parallelism whenever exploitable. This provides further motivation to potentially move low randomness usage from a primary to a secondary design goal in hardware masking research.

This work is licensed under a "CC BY 4.0" license. Date of this document: 2024-06-17.

E-mail: gaetan.cassiers@uclouvain.be (Gaëtan Cassiers), loic.masure@lirmm.fr (Loïc Masure), charles.momin@uclouvain.be (Charles Momin), thorben.moos@uclouvain.be (Thorben Moos), amir.m oradi@tu-darmstadt.de (Amir Moradi), francois-xavier.standaert@uclouvain.be (François-Xavier Standaert)

<sup>&</sup>lt;sup>a</sup>Work performed in parts during a post-doctoral stay at IAIK, TU Graz, Graz, Austria.

Keywords: Hardware Masking · Randomness · Side-Channel Analysis · Trivium

# 1 Introduction

Side-channel analysis is known to be a significant threat to implementations of cryptographic algorithms and protocols that must operate under adversarial exposure. If untrusted individuals gain physical access to a cryptographic device, measurable quantities such as power consumption or electromagnetic emanations during the processing of secret material can be monitored to extract sensitive information. This type of attack was first demonstrated by Kocher et al. in 1999 [KJJ99] and has since inspired a great deal of research on the theory and practice of implementation security. Masking (also known as secret sharing) is a well-known countermeasure to protect cryptographic implementations from side-channel analysis adversaries. It was first proposed by Chari et al. in 1999 [CJRR99], and is nowadays widely considered to be the most potent protection mechanism against passive physical adversaries. Its core principle is based on splitting each potentially sensitive intermediate variable into a discrete number of shares, in such a way that only the combination of all shares reveals information about the secrets. Using this technique, adversaries can be forced (implicitly or explicitly) to collect information on all individual shares before combining them to reconstruct the sensitive intermediates. Yet, learning information about the secrets from partial information on their shares is a hard problem. To be precise, if the leakage of the individual shares is sufficiently noisy and independent, masking is capable of providing exponential security in the number of shares against adversaries trying to extract sensitive information from side-channel observations see [PR13, DDF14, DFS15] for respective formalizations. The implementation overheads of masking are typically estimated to be quadratic in the number of shares due to the known complexity of masked multiplications [ISW03].

Yet, and especially when masking is applied to hardware implementations of cryptographic algorithms, the independence assumption is often invalidated by physical defaults such as glitches [MPG05], transitions  $[CGP^+12]$  and couplings  $[CBG^+17]$ . It has taken the research community several years to develop generalizable strategies to avoid these issues at the conceptual level. The first solid approaches toward preventing glitches from recombining shares in hardware masking schemes came in the form of threshold implementations [NRR06, NRS08]. A few years later, other masking schemes with a lower number of shares to achieve a given protection order (compared to threshold implementations) were proposed [RBN<sup>+</sup>15, GMK16, GMK17, GM17]. These schemes also targeted higher-order security for the first time, after it was found that higher-order threshold implementations suffered from conceptual flaws [BGN<sup>+</sup>14a, Rep15, RBN<sup>+</sup>15]. Simultaneously, independent researchers started investigating the requirements needed to securely compose masked building blocks into arbitrary cipher implementations, resulting in the security notion of Strong Non-Interference (SNI) [BBD<sup>+</sup>16]. Following these advances, the robust probing model was introduced to allow formal analysis of composability and robustness against physical defaults jointly [FGP<sup>+</sup>18]. Subsequently, it was shown at CHES 2019 that many previously proposed hardware masking schemes suffer from composability flaws under the robust probing model at higher orders, giving substantial evidence that a formal analysis is beneficial to properly generalize schemes to arbitrary orders [MMSS19]. Finally, in 2020, a new composability notion called Probe Isolating Non-Interference (PINI) was introduced to allow trivial composition of masked implementations of linear and non-linear functions [CS20, CGLS21]. Based on this notion, new masked gadgets have been introduced [CGLS21, KM22b, KM22a] along with tools that allow formal verification of their properties [KSM20, CGLS21] and automated generation of full masked hardware circuits based on PINI gadgets [KMMS22].

#### 1.1 Motivation

Clearly, the past few years have advanced our collective understanding of how to best capture physical defaults such as transitions, couplings, and glitches through proven design principles. This, in turn, enables fast and efficient masked hardware implementations that can leverage parallelism to simultaneously operate on the individual shares of a secret intermediate without sacrificing security against physical adversaries. In order to achieve this symbiosis between performance and security, hardware masking schemes often consume a notoriously large number of random bits per cycle. Indeed, in the past several years, a strong trend is observable in the community towards constructing masked hardware implementations entirely from circuit gadgets that are provably robust probing secure and composable (e.g., [CS21, KSM22, MCS22, KMMS22]). This is done in order to automatically derive guarantees that the resulting full hardware implementations are provably secure themselves. The gadgets used for this purpose typically consume a certain amount of fresh random bits per clock cycle to satisfy the required properties, e.g., d(d-1)/2bits for one 2-input AND gate with d shares in domain-oriented masking [GMK16] or HPC2 [CGLS21]. Naturally, full ciphers composed of many such gadgets also need many bits of fresh randomness per cycle, especially if those implementations leverage parallelism, are optimized for low latency and if higher-order protection is required. Hence, it is not uncommon for parallel masked hardware implementations of full block ciphers to require hundreds or even thousands of independent, uniformly distributed, and unpredictable random bits per cycle. Recent works presented at CHES 2022 [KMMS22] and CCS 2022 [KM22b] list exemplary cost and performance figures for masked round-based cipher implementations that demand multiple thousands of freshly random bits in each cycle. Even for serialized implementations or single S-boxes it is not uncommon to see requirements in the range of hundreds of bits per cycle. Despite this huge demand, most works on the topic have considered the efficient generation and distribution of these bits to be beyond their scope. In fact, the majority of publications in the masking literature simply assumes the existence of robust and high-entropy randomness sources. We argue that the lack of focus on this topic can have negative consequences, since concurrent randomness generation is a crucial part of masked implementations, especially in hardware. Failing to include this component in the evaluation of masking schemes clearly leads to a poor understanding of the efficiency vs. security tradeoff of secure implementations.

#### 1.2 Research Question

Our work aspires to answer the question whether such huge demands for randomness can be satisfied in hardware and at what cost, as this aspect has been neglected in most previous publications. While reducing randomness requirements is an often researched topic (initiated in [BBP<sup>+</sup>16], with many follow-up works), studies of the actual cost of randomness for masking are surprisingly missing in the literature. For example, the authors of the recent [KM22a] consider quite different approaches in order to provide meaningful comparisons between masking schemes including randomness generation, such as an individual 32/64-bit LFSR for each bit of randomness required per cycle or a Keccakbased PRNG, which both turn out to be rather expensive. Hence, it is our goal to find more efficient solutions while also clarifying the relevant security properties that must be satisfied in the masking context.

Once a reliable estimate of the cost of producing a certain number of random bits per cycle is established, it becomes much easier to decide on crucial trade-offs in masked hardware implementations. Additionally, it will help to answer the question whether schemes that minimize randomness requirements are more worthwhile, or whether it is better to optimize other parameters such as latency or area at the cost of higher randomness usage.

# 1.3 TRNG vs. PRNG

Whenever randomness is required in a design, at least some initial entropy must come from a true randomness/noise source, usually extracted by a True Random Number Generator (TRNG). Yet, as we will confirm in the paper, TRNGs tend to be either fairly slow or resource-hungry, making the cost of generating each truly random bit significant. Thus, it is a common strategy to use Pseudo Random Number Generators (PRNGs), which are generally considered to be much more efficient than TRNGs, to stretch the initial seed (obtained once at power-up) into many pseudo-random bits whenever needed during runtime.

#### 1.4 Requirements for Masking Randomness

Many different PRNG constructions have been proposed in the literature for a variety of applications. Of course, depending on the concrete use case, different properties are required from the random numbers. Cryptographically strong PRNGs, as required in many cryptographic protocols for generating keys, nonces or salts, should produce outputs that are indistinguishable from genuine randomness for computationally bounded adversaries. However, the requirements are not always that strong. In the concrete case of masking, adversaries typically cannot directly obtain the output of the PRNG. In fact, there is no output that depends on the generated random bits at all, since these values are only used for internal randomization of intermediate computations, and the final results of the masked operations are unmasked internally before being released to outside observers. Hence, adversaries can only obtain a noisy version of the generated random bits from their sidechannel observations (especially noisy in hardware if generated in parallel to the masked cipher implementation), leaving the possibility to perform direct state recovery attacks on the PRNG quite theoretical (see [JD06, BMV07, CMM14, MCB<sup>+</sup>22]). As a result, many previous works have opted for random number generators without cryptographic strength for mask generation, such as Linear Feedback Shift Registers (LFSRs).

LFSRs are arguably the most simple primitive for generating long non-repetitive sequences of random-looking, uniformly distributed bits from an initial seed. However, as mentioned above, LFSRs cannot provide black-box security, and their linear output can be distinguished from true randomness using statistical test suites such as the one proposed by the National Institute of Standards and Technology (NIST) [BRS<sup>+</sup>10]. This raises doubts regarding their suitability to fill the two main requirements for (pseudo-)random numbers in masking contexts, namely 1) uniformity and 2) unpredictability [GSF13]. Without uniformity, most masking schemes cannot keep their security promises. Even a small bias in the sampling of random masks can lead to a reduction of the protection order, despite noise and independence assumptions being fulfilled. Low Entropy Masking Schemes (LEMS) initially attempted to relax such requirements on the quality of random numbers in order to reduce costs while still maintaining the security order. However, these schemes had to make additional assumptions which have been demonstrated to not always hold in practice [GSP13, YE13]. The need for unpredictability of random numbers is even more obvious in masking contexts. If an adversary can predict the random bits and has knowledge of the data being processed (known-plaintext scenario), she can compute all intermediate values that are actually processed inside the cryptographic implementation and perform attacks in the same trivial way as on unprotected circuits. Since all future outputs (at least until the next re-seeding) can be calculated once the internal state of a deterministic PRNG is discovered, state recovery attacks are commonly the most relevant threat to the unpredictability requirement. With respect to LFSRs, once an adversary has obtained a sufficient number of consecutive output bits, state recovery is trivial. More precisely, if the feedback polynomial is known – with m being the LFSR's degree – an attacker only needs to observe m consecutive output bits to know its internal state and

predict all further outputs. When the feedback polynomial is unknown, the attacker typically requires 2m consecutive output bits [PP10]. However, as mentioned before, the attacker model in the context of masking does not allow direct access to the generated random bits, making the application of such attacks difficult for sufficiently noisy leakages.

#### 1.5 Masking Randomness in Previous Works

In the state-of-the-art hardware masking literature, researchers have used various techniques to generate the random bits required for their experimental analyses. An AES-128 in counter (CTR) mode has been used in [BGN<sup>+</sup>14b] to provide 44 random bits per clock cycle. Assuming that a round-based AES-128 implementation requires at least 12500 gate equivalents (GE) of area (the smallest value listed in the comparison of [UHM<sup>+</sup>20]) and produces 128 output bits every 10 clock cycles, the area cost of generating one random bit per cycle can be estimated to be at least 977 GE. Other works like [CRB+16] instantiated reduced-round variants of the low-latency cipher PRINCE [BCG<sup>+</sup>12] in Output FeedBack (OFB) mode to rapidly generate a high number of random bits per clock cycle. It is not stated how many of the PRINCE rounds were removed, but calculating based on a full PRINCE as unrolled implementation which requires approximately 8 000 GE [BCG<sup>+</sup>12] of area and generates 64 output bits per cycle, the cost of generating one random bit per cycle is about 125 GE. For a round-reduced variant, this cost might be halved at the expense of a reduced security level. In [SBHM20], a sponge-based PRNG [BDPA10] using a variant of Keccak [BDPA13] is used to generate 976 random bits every clock cycle. The design details provided are insufficient to estimate the cost per bit of the concrete construction used. However, a round-based Keccak-f[200] permutation requires about 5 000 GE of area and runs for 18 clock cycles [KY10]. Using the construction proposed in [BDPA10], either 64 or 96 bits are obtained per call to Keccak-f[200], resulting in a minimum cost of 938 GE to produce one random bit per cycle. As mentioned earlier, there are also a number of works that use LFSRs to generate random values for masking. For instance, 31-bit LFSRs are employed in [MMW18, Moo19, SM21, KMMS22, KSM22] in such a way that each required random bit is generated by a dedicated LFSR that is randomly seeded on power-up. Following the same principle, the authors of [KM22a] have considered such a 31-bit LFSR, a 64-bit LFSR, and different variants of Keccak-Sponge-based PRNGs, and have reported the overhead of a hardware masking scheme including the area required for the necessary PRNGs. The cost of generating one random bit per cycle is estimated as 286 GE and 565 GE for the 31-bit and 64-bit LFSRs respectively [KM22a]. Further, it has been explored in  $[PYR^+16]$  whether evolutionary computation can be beneficial in the design and optimization of lightweight PRNGs for masking applications. The authors have proposed multiple PRNG variants that have passed all tests of the NIST statistical test suite  $[BRS^{+}10]$ . The most efficient one, based on Cartesian genetic programming, is said to have a throughput-area ratio of 68.14 Mbps/GE based on the NanGate 45 nm library. While this is significantly more efficient than all other approaches mentioned above, it is entirely unclear whether this primitive provides sufficient resistance against modeling or state-recovery attacks. Indeed, the variants proposed by the authors which are claimed to be prediction resistant are significantly more expensive. Finally, one work on multiplicative masking of the AES has applied an unrolled Trivium instance to generate multiple random bits per cycle for masking [MRB18]. The use of Trivium is only mentioned at the end of the work's Appendix, without any further reasoning or cost analysis. Yet, the concrete properties of this approach are investigated in detail in Section 3.

## **1.6 Our Contributions**

In this work, we focus on the problem of efficiently and securely generating randomness in hardware with properties suitable for use in masked implementations. As a first step, we briefly investigate the efficiency of state-of-the-art on-chip TRNGs, focusing mainly on a high-throughput, low-area TRNG proposed at CHES 2018 [YRG<sup>+</sup>18]. While this design appears to offer promising performance compared to its competitors, we discard the possibility of using only TRNGs for the entire randomness generation due to their suboptimal cost-performance trade-off, which stays orders of magnitude behind that of PRNGs. In consequence, we conclude that PRNGs are indeed preferable in the considered setting, especially when trying to satisfy the needs of randomness-hungry masked parallel hardware implementations, as we focus on in this work. Accordingly, we then analyze a number of efficient cryptographic building blocks based on their throughput-area ratio with potential for constructing secure PRNGs tailored to efficient mask generation. The considered building blocks are selected in part based on prior reports comparing the 32 primitives that survived to Round 2 of NIST's Lightweight Cryptography (LWC) standardization process [oSN17] and the 8 stream ciphers in Profile 2 (hardware) that reached the final phase of eSTREAM, the ECRYPT stream cipher project [oEiCE04]. In particular, we have included in our comparisons:

- The lightweight primitive *Subterranean 2.0* [DMMR20], which offers by far the best throughput-area ratio among NIST LWC Round 2 candidates according to [AZ21].

- The cross-platform permutation *Gimli* [BKL<sup>+</sup>17], which is among the highest throughput primitives of NIST LWC Round 2 candidates according to [AZ21].

- The ultra low-latency block cipher *SPEEDY* [LMMR21], whose variant **SPEEDY-5-192** is claimed to provide the best throughput-area ratio among low-latency ciphers.

- The stream ciphers *Trivium* [Can06, CP08] (and its variants Bivium B [Rad06] and Kreyvium [CCF<sup>+</sup>16]), *Grain v1* (both 80- and 128-bit variant) [HJM07, HJMM06] and *MICKEY 2.0* (both 80- and 128-bit variant) [BD08] which are the three primitives most frequently listed as best performers in throughput-area ratio among the eS-TREAM competition's Phase-3 candidates, according to a number of different comparative efforts [GB08, GLB<sup>+</sup>06, BKSQ07, GSB07, Rog07, HCK<sup>+</sup>08, KSPS13, LLL20].

Where possible, we also consider reduced-security variants of these primitives, motivated by the assumption that full cryptographic strength may not be required in our target setting, i.e., randomness used in masking. For Gimli and SPEEDY this means that we consider reduced-round versions. For Trivium, we consider its reduced-security variant Bivium B [Rad06], which has been introduced to study the cryptanalytic properties of Trivium. For Grain v1, both the 80- and 128-bit variant, we consider reduced versions where the NLFSR part is removed and only the filtered LFSR part remains, in order to include a representative of that class of primitives in the comparison. To the best of our knowledge, such reduced versions have not received any independent cryptanalysis and are likely insecure, considering that fast correlation attacks targeting the filtered LFSR part have been used to successfully break all complete Grain v1 versions  $[TIM^+18]$ . Finally, despite the fact that LFSRs are lacking any black-box security due to the linear dependency between their produced output bits (and are thus generally considered a poor choice for random number generation in cryptographic contexts), we include them in our comparison and discuss the security implications of employing such primitives for mask generation experimentally. Hence, we believe that our comparison covers the entire spectrum from candidates that are trivially insecure in the black-box setting but most efficient, to those which are cryptographically strong but less efficient, in order to identify the most promising primitives.

As part of our investigations, we observe that in order to maximize the throughput-area ratio, different implementation styles are best suited for different designs. For permutations and block ciphers, round-unrolled pipelined implementations usually lead to good results,

$\mathbf{6}$

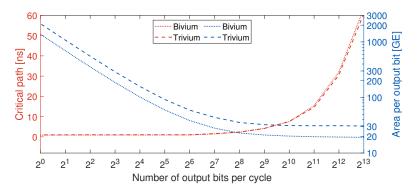

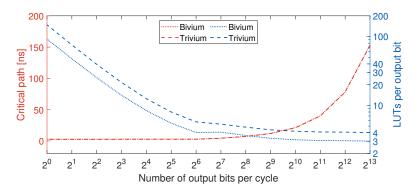

while for stream ciphers and LFSR-based primitives unrolling multiple update/feedback functions to generate several output bits in a single cycle using a single hardware module seems most promising (see [GB08, GLB<sup>+</sup>06, GSB07, Rog07, HCK<sup>+</sup>08, MS11, LLL20] and explanations in Section 3). Since the degree or level of unrolling can be chosen arbitrarily for stream ciphers, these primitives offer a high flexibility to hardware designers. However, the effectiveness of unrolling a stream cipher implementation to actually maximize its throughput-area ratio depends heavily on the concrete cipher design. Thanks to the fact that Trivium's update/feedback function is independent of the last 64 output bits produced, leading to high efficiency for even large unrolling levels, our throughput-area ratio comparison leaves no doubt that Trivium is the most efficient cryptographically strong primitive among our selected candidates, outperforming the other black-box-secure designs by an impressive margin.

Only LFSRs, when also unrolled to produce multiple bits simultaneously, are able to outperform Trivium, Bivium B and Kreyvium. Hence, we take a closer look at unrolled LFSRs from a security perspective in the relevant application setting. In this respect it is noteworthy that, to the best of our knowledge, no previous work has claimed that the use of *unrolled* LFSRs to generate randomness for masking is secure or advisable. The authors of [KM22a] for example discussed the need to use an independent LFSR for each random bit required per cycle in a masked circuit, and all related previous works have apparently followed the same strategy. However, according to our comparison, this is not a cost-effective solution as it proves more costly than multiple of the cryptographically strong candidates we analyze (i.e., there is little incentive to ever consider those in practice). Therefore, we focus on the security properties of *unrolled* LFSRs in two case studies, and find that without great care, this strategy can lead to problems when used in masked implementations, and may cancel the entire side-channel security. In fact, the demonstrated problems extend, although in limited form, to the single-LFSR-per-bit scenario which has more commonly been considered in the past (potentially causing multivariate instead of univariate leakage though). Besides, we also put forward weaknesses in the original masking PRNG design of the OpenTitan project. Multiple independent 32-bit filtered LFSRs were originally instantiated to be used for generating the randomness needed for the masked AES core. We describe in detail how state recovery of such a PRNG is possible with low data complexity by enumerating all possible states of the LFSRs separately which allows to generate all previous and future masks. The OpenTitan design team has acknowledged and confirmed the vulnerability and is determined to switch to a Bivium/Trivium-based alternative to increase the security at very low overhead ( $\approx 1.8\%$  for the total masked AES core) in the near future.

We insist that it is not our goal to suggest that (unrolled) LFSRs can never be used securely for mask generation. We are confident that this can be achieved (as long as state guessing and correlation attacks [Can11b] are not a concern due to insufficient size) when ensuring that each random bit is used only in positions where it cannot cause problems. Yet, our case studies provide evidence that when using such linear primitives which lack black-box security guarantees, the randomness generation and the masking scheme must be analyzed jointly. Moving to primitives that offer black-box security, such as Trivium, solves this issue and allows the independent analysis of the masked implementation and the randomness generator, which is significantly more convenient from the designer's and evaluator's perspective. In other words, we claim that (unrolled) LFSRs are not sufficient for masking in general and therefore warn against their use, not that they cannot be used in specific and carefully crafted case studies. Yet, in view of the limited overheads shown by unrolled stream ciphers like Trivium (for high security levels) and Bivium B (for medium security levels), we recommend them as a good default option for the efficient generation of randomness for masked hardware implementations. We detail how to use these primitives, discuss their security against side-channel attacks, and finally estimate the

resulting cost of generating n random bits per cycle. For Trivium, the asymptotic cost per random bit updated per clock cycle is about 30 GE on ASIC or 4 LUTs on FPGA. Using Bivium B, the cost can even be reduced to 20 GE or 3 LUTs per random bit. These results show that randomness generation is significantly cheaper than estimated in most previous works, which incentivizes highly parallel (low latency) masked hardware implementations and might motivate researchers to focus on alternative optimization goals than reducing randomness usage in masking schemes. We believe that our conclusions are of positive nature for the physical security community, as implementations using many random bits per cycle are also known to provide superior security levels against more sophisticated adversaries (e.g., so-called horizontal attacks [BCPZ16]) compared to low-randomness approaches.

# 2 Background

In this section, we introduce primitives that are commonly considered to generate randomness for masked implementations. We start with a quick look at TRNGs, then move to LFSRs and PRNGs (including stream ciphers), before discussing the design details of Trivium and Bivium. We conclude by describing how stream cipher implementations can be unrolled.

# 2.1 True Random Number Generators (TRNGs)

Whenever randomness is needed in a digital design, at least some initial entropy has to come from an analog noise source, as deterministic digital computation methods are unable to generate true randomness. Thus, TRNGs exploit noise sources based on physical phenomena with unpredictable behavior. An optimal source of entropy would be radioactive decay, since the timing of events at the atomic level is impossible to predict, even with unbounded memory and computational resources. Yet, it is clearly not realistic to sample radioactive decay in integrated circuits to generate random numbers for cryptographic applications. Instead, noise sources inherent to modern integrated circuits are commonly leveraged. These include clock jitter, metastability, thermal noise in resistors, oscillatory metastability, write collisions in dual-port random access memories and random initialization of bi-stable circuits [FD02, FL14]. A large number of TRNG designs based on these physical phenomena is discussed and compared in [PMB<sup>+</sup>16, YRG<sup>+</sup>18]. The raw random numbers extracted from entropy sources are typically subject to statistical defects and need to be tested and post-processed before being used in applications. Obtaining independent random values with high entropy is therefore a laborious process that comes at a significant cost (e.g., in latency or area).

#### 2.2 Linear-Feedback Shift Registers (LFSRs)

LFSRs are structures that hold an array of bits shifted one position per step in a certain direction. The bit that gets shifted out of the array is typically the output, and the new bit shifted into the array is determined by a feedback function computing a linear combination of a number of state bits. LFSRs consist of clocked storage elements like flip-flops, and the feedback function is typically described by a polynomial. The number of storage elements is the degree of the LFSR. The maximum period, or sequence length, of an LFSR of degree m is  $2^m - 1$ . LFSRs with maximum period exist for any degree m. Since the LFSR output is determined by a linear combination of the initial state bits only, state recovery attacks are trivial once a sufficient number of consecutive output bits are observed (2m if the feedback polynomial is unknown; m otherwise [PP10]). Due to this lack of black box security, LFSRs are rarely used as standalone PRNG primitives

8

in cryptographic applications but more commonly as useful ingredients (e.g., for stream ciphers – see next). Yet, they are named frequently for the generation of randomness to be consumed by masked implementations.

## 2.3 Pseudo-Random Number Generators (PRNGs)

Due to the high cost of generating *true* random values in integrated circuits, it is common practice to use PRNGs to stretch short sequences of true random bits (called seeds) into long sequences of pseudo-random bits. PRNGs are deterministic polynomial time algorithms constructed from an iterated function [BM82]. They generally use a pair of functions f and g, where  $f: \{0,1\}^n \to \{0,1\}^n$  iteratively updates an n-bit state  $s_i = f^i(s_0)$ , and  $g: \{0,1\}^n \to \{0,1\}^m$  generates the output bitstream  $g(s_0)||g(s_1)||\dots$  The initial state  $s_0$  is derived from the seed, which can be obtained from a TRNG at device power-up. Therefore, all the entropy in the output descends from the initial random seed, and is further limited by the state size of a PRNG. Cryptographically strong PRNGs, required for key or nonce generation in many cryptographic protocols – when properly seeded – should produce output indistinguishable from genuine randomness for all computationally bounded adversaries.

PRNGs are natural candidates to generate randomness for masked implementations since they generally have good security properties in presence of leakage due to the continuous update of their secret state [YSPY10]. Furthermore their initialization, that may lead to stronger side-channel attack vectors if it had to be synchronized with another communication party  $[SPY^+10]$ , is not needed in this context and can be replaced entirely by a truly random seed of sufficient length generated on-chip. As most cryptographic primitives, they can be obtained generically from well-investigated building blocks like (tweakable) block ciphers (as in the previous reference) or permutations [BDPA10] – both possibly coming with similar guarantees in terms leakage-resistance [BBC<sup>+</sup>20]. They can also be obtained from dedicated constructions, usually introduced as stream ciphers. Such dedicated constructions generally correspond to a slightly more aggressive security (margins) vs. efficiency tradeoff compared to generic constructions. The latter appears appealing for our purposes since expensive randomness generation makes the application of higher-order masking prohibitive and, as already mentioned, the adversarial scenario of this generation is different from the stream cipher one (i.e., the adversary sees only the leakage of the PRNG). Concretely, we will primarily investigate Trivium [oEiCE04, Can06] and its Bivium B variant [Rad06] that we detail next. We will also report performance figures for Subterranean 2.0 [DMMR20], Gimli [BKL<sup>+</sup>17] and SPEEDY [LMMR21]. The former two are high-throughput candidates from the NIST lightweight cryptography standardization process [oSN17], while the latter is a performance-driven block cipher with few rounds. For completeness, we also include the stream ciphers Grain v1 [HJM07] and MICKEY 2.0 [BD08], as well as Kreyvium which is a variant of Trivium with 128-bit security  $[CCF^+16]$  in our comparisons.<sup>1</sup>

### 2.4 Trivium & Bivium

Trivium is a stream cipher submitted by De Cannière and Preneel to the eSTREAM competition, a multi-year effort to collect compact stream ciphers suitable for widespread adoption [oEiCE04, Can06]. It was selected to be part of the final portfolio [CP08] and has later been standardized as part of the lightweight stream cipher standard ISO/IEC 29192-3. Trivium is based on a combination of three Non-Linear Feedback Shift Registers (NLFSRs) of degree 93, 84 and 111 (288 bits in total) – see Figure 1 for an illustration. It has two input parameters, an 80-bit key and an 80-bit initialization vector (IV). As

$<sup>^1</sup>$  We do not provide the details of these additional algorithms due to place constraints.

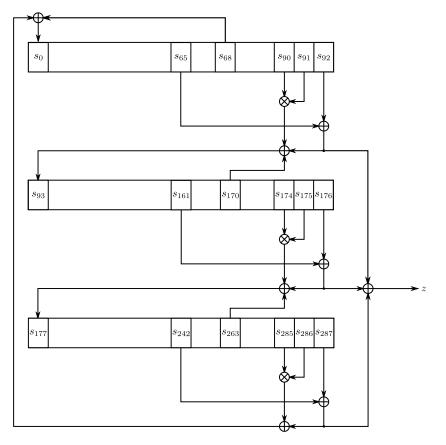

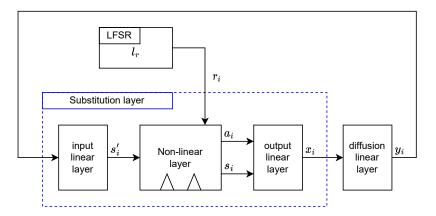

Figure 1: Schematic of the Trivium stream cipher consisting of 3 NLFSRs.

is common in cryptographic applications, the IV is public, but should take a new value for each encryption session. During the initialization phase, the IV is loaded into the 80 leftmost positions of the upper register, while the key is loaded into the 80 leftmost positions of the middle register. All other bits are set to zero, with the exception of the three rightmost bits of the bottom register, which are set to one. The cipher is then clocked for 1152 steps without producing any keystream, which corresponds to 4 rotations of the state ( $4 \cdot 288 = 1152$ ), that randomizes the content of the registers. After the initialization phase (also called warm-up) is completed, the online phase begins and the keystream is generated. According to the performance comparisons of phase-3 candidates of the eSTREAM competition presented in [GB08, GLB<sup>+</sup>06, BKSQ07, GSB07, Rog07, HCK<sup>+</sup>08], unrolled Trivium offers by far the best throughput-area ratio for hardware implementations.

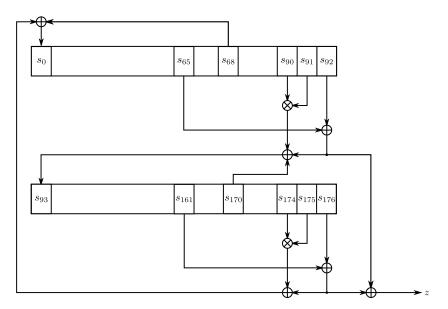

In an attempt to better understand the security of Trivium, Raddum introduced two reduced variants, called Bivium A and Bivium B [Rad06]. Both of them consist of only two of Trivium's NLFSRs, namely the 93-bit and the 84-bit ones. Bivium B is depicted in Figure 2. In Bivium A, the keystream is generated as the sum of 2 state bits, both from the same register. In Bivium B, the keystream is generated as the sum of 4 state bits, 2 from each NLFSR. While no key recovery attack on Trivium with a complexity below  $2^{80}$  is known, there have been effective attacks on both Bivium variants. In 2006, Haddum presented an attack to break Bivium A in about a day [Rad06] by building and solving a system of equations using the output keystream with the initial state bits as the unknowns. He estimated the same attack to require about  $2^{56}$  seconds (about  $2^{31}$  years) on Bivium B. Later in 2007, Maximov and Biryukov presented an attack on Bivium B with complexity  $c \cdot 2^{37}$ , where the constant c denotes the time required to solve a system

**Figure 2:** Schematic of Bivium B, a reduced security variant of the stream cipher Trivium consisting of 2 NLFSRs.

of equations (estimated to be  $c \approx 2^{14}$ ) [MB07]. In 2011, it was reported in [HL11] that by guessing 35 variables, Bivium B can be solved in  $2^{32.81}$  seconds (about 7.9 years) by MFCS, an algorithm for solving Boolean polynomial equations. In 2019, a key-recovery attack on Bivium B based on Boolean equation solving has been reported [SSD19]. The concrete complexity of the attack is unclear due to ambiguous claims in the paper, but the authors state that about 4 terabytes of memory and a parallel search over  $2^{39}$  threads is required to recover the initial state and the key. We conclude that Bivium A is trivially insecure and that Bivium B can be broken in practical time complexity on large computation clusters. In the rest of the paper we denote Bivium B as Bivium and use it as an aggressive design that may be secure in the leakage-only setting, to gauge the performance gains that such an optimization offers.

# 2.5 Unrolling Stream Ciphers

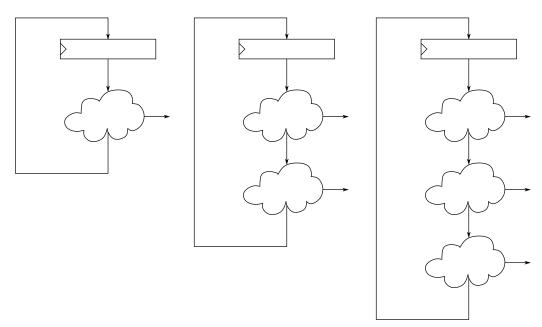

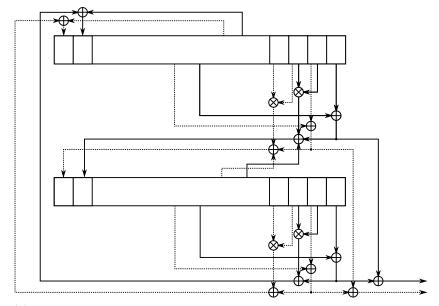

While the terminology of *unrolling* a stream cipher may not be widely established (although it has been used in previous works [BMA<sup>+</sup>18]), the general concept is well known for many years. Sometimes it has only been described using different terms. Stream ciphers like Trivium and Grain have been developed with this implementation trick in mind in the early 2000s already. Similar to the iterated round functions of a block cipher or permutation, the (normally consecutively executed) state update (and output) functions of a stream cipher can be unrolled, which means multiple instances are realized in hardware without any memory elements in between so that the combinatorial logic of multiple steps is evaluated in a single cycle. See Figure 3(a) for an exemplary illustration of unrolling an update function. Here, each instance of the update function is producing 1 output bit or word per cycle (different from the block cipher analogy). While this is obviously a convenient instrument to adjust the tradeoff between latency (in cycles) and critical path (in seconds), there is another big advantage in the case of stream ciphers. Much unlike typical round functions of block ciphers and permutations, the state update functions of stream ciphers (typically) produce only 1 bit/word per cycle and are often chosen to be sparse. Sparsity of the function means that it receives only a few selected bits/words as inputs instead of the entire state. Thus, when choosing the function in a clever way, namely that the next

update function does not receive the current feedback bit as input, it becomes possible to unroll a certain number of consecutive state updates (i.e., compute them in parallel in one cycle) without directly increasing the logic depth or critical path of the circuit. See Figure 3(b) for an example of a 2-bit unrolled Bivium implementation where the gate depth is not changed compared to the regular design in Figure 2. It turns out stream ciphers like Trivium and Grain [HJM07, HJMM06] indeed employ well-chosen functions to allow fast implementations generating multiple output bits and performing multiple updates per clock cycle. Trivium's update function ensures that any state bit which has just been modified is not used for at least the 64 following update steps [CP08]. For Grain v1 with 80-bit key, modified state bits are not used in the next 16 updates [HJM07] while for the 128-bit key variant that number is even increased to 32 [HJMM06]. Consequently, the critical path is only increased in steps of 64, 16 and 32 bits of unrolling, respectively. The area, however, is increased for each additional copy of the function. Yet, as only the combinatorial logic needs to be replicated and as the area of stream ciphers like Trivium and Grain is highly dominated by the state register(s), unrolling these primitives corresponds to a net gain in throughput-area ratio up to a certain level. Furthermore, even beyond that level, the bits/cycle metric continues to grow much faster than the critical path of the implementation.

We acknowledge that our definition of *unrolling* has been mostly been referred to as *parallelization* in previous works on stream cipher implementations [GB08, GSB07, Rog07, LLL20]. We have decided to avoid this term in our work, as it conflicts with the description of multiple unrolled stream ciphers in parallel, which is a concept we need later in Section 5. Less commonly, unrolled stream cipher circuits have also been referred to as *higher-radix* implementations (e.g., radix-64 for 64-bit unrolled Trivium) [GLB+06, HCK+08]. An FSE 2019 work on the energy efficiency of stream ciphers has used the term unrolling in the same way that we do, and additionally also explored large unrolling factors in order to optimize the implementation properties of stream ciphers for certain settings [BMA<sup>+</sup>18].

# 3 Cost Efficiency Comparison

In the following we explore the suitability of multiple building blocks to be used as randomness generators for masked hardware implementations from the performance viewpoint.

## 3.1 Throughput-Area Ratio

Comparing primitives for cost-efficient randomness generation begs the question which performance metric is the most relevant to evaluate. Since we aim to satisfy the randomness demands of even large, parallel, higher-order masked hardware implementations of cryptographic algorithms, we argue that the throughput-area ratio (TPA) is one of the most meaningful metrics to look at. While a small default area and a low power consumption (as well as combined metrics of them with the throughput) can also be of high importance, we believe that TPA is the most universally relevant quantity to answer common questions in the envisioned application setting. Assuming a masked implementation requires up to 1000 fresh random bits per cycle (not unusual for gadget-based parallel higher-order implementations, c.f. [KMMS22]) at 100 MHz in 65 nm ASIC technology, the TPA is arguably the most suitable metric to find the cheapest solution for generating the required amount of randomness per cycle at the desired clock frequency. For concrete settings, the throughput-area ratio measured in (bits/cycle)/GE is probably ideal for decision making. Yet, it is not best suited for general comparisons of multiple candidates due to its strong dependency on the chosen frequency and implementation technology. Indeed, to obtain both fair and optimized results in the (bits/cycle)/GE metric for any given candidate, a separate implementation needs to be constructed to best leverage the available critical path budget

(a) 1-bit/1-word (left), 2-bit/2-word (middle) or 3-bit/3-word unrolled update functions.

(b) 2-bit unrolled Bivium, producing keystream at twice the rate as regular Bivium.

**Figure 3:** Unrolling a stream cipher like Trivium/Bivium is achieved by implementing multiple consecutive update functions in the same hardware circuit, each producing one output bit/word per cycle. If one update function's inputs are independent of the feedback bits of multiple previous update functions, consecutive steps can be unrolled without increasing the circuit depth (e.g., up to 64 steps for Bivium/Trivium/Kreyvium).

at each considered frequency and for each considered implementation technology. When measuring the throughput-area ratio in (bits/s)/GE instead, the critical path delay is part of the formula and it becomes easier to compare multiple candidates without limiting the analysis to one predefined setting. In fact, the (bits/s)/GE value can be seen as an upper

bound on the TPA in the sense that the optimal value is obtained for a concrete circuit under the assumption that the operating frequency of the device is determined by this implementation, instead of the implementation being tailored to one predefined frequency. As not every candidate will fit into each setting perfectly, flexibility of an implementation is another important factor. In the following we use the throughput-area ratio measured in (bits/s)/GE to compare the selected candidates for concurrent randomness generation. We aim to avoid remaining technology biases by evaluating the metric in multiple standard cell libraries for the PRNG building blocks.

# 3.2 High-Throughput Low-Area TRNG

Since an efficient TRNG implementation is always needed when randomness has to be generated inside an integrated circuit, the first important question to answer is whether this primitive can potentially be used for all randomness generation, which would save the cost of implementing a PRNG in addition. To answer this question, we have selected a suitable representative from the TRNG literature and evaluate its efficiency in the following. At CHES 2018, Yang et al. proposed a high-throughput, low-area TRNG suitable for both ASIC and FPGA implementations [YRG<sup>+</sup>18]. The design is called ES-TRNG, where ES stands for Edge Sampling. The chosen noise source is timing jitter, and the design relies on two techniques that the authors call variable-precision phase encoding and repetitive sampling to increase throughput and reduce area. We implemented this design using a 65 nm low-power CMOS standard cell library and obtained the results listed in Table 1. The throughput is estimated in part based on timing jitter measurements on a test chip manufactured under the same 65 nm technology and in part based on a prototype FPGA implementation whose output has been evaluated positively by statistical test suites. For a 100 MHz system clock the resulting throughput when synthesized in (and parametrized for) 65 nm ASIC technology is 2.2 Mbit/s and thus higher than the 1.15 Mbit/s given in [YRG<sup>+</sup>18]. This is expected when moving from FPGA to ASIC implementation. In fact, higher performances are likely still possible on ASIC platforms. Our concrete implementation is able to produce 7.4 kbit/s of high-entropy random numbers for each gate equivalent (GE) of area (i.e., a TPA of 7.4 (kbit/s)/GE). Please note that a recent improvement of the original ES-TRNG design has been published in [LBS22] under the name Tight-ES-TRNG. The authors performed low-cost optimizations to ensure that the signal edges populate a larger portion of the full distribution of phase jitter to increase the achievable entropy level. In that work, the throughput is increased to 5.6 Mbit/s. Even higher throughput may potentially be achieved with alternative TRNG designs according to the comparisons presented in [PMB<sup>+</sup>16, YRG<sup>+</sup>18], at the cost of a significantly larger area and less freedom in the implementation. In particular, the only TRNG design listed which provides a larger throughput-area ratio compared to the ES-TRNG is a Self-Timed Ring (STR) based TRNG [CFAF13, CFFA13], with an approximately 6 times better efficiency [PMB<sup>+</sup>16, YRG<sup>+</sup>18]. However, this design occupies a 20 to 30 times larger area (high default cost) and requires both manual placement and manual routing. Even when considering such a design, the throughput-area ratio would still fall in the range of tens, maybe hundreds, of kbit/s/GE for a 65 nm ASIC implementation, without yet considering the cost of monitoring the entropy source or continuous internal testing. We demonstrate in the rest of this section that it is possible to implement cryptographically strong PRNGs with a much higher throughput-area ratio than that, providing strong support for the idea that randomness-hungry masked implementations are better served by PRNGs than TRNGs.

|         | Min. Area        | Min. Latency          | Throughput @ $100\rm MHz$ |

|---------|------------------|-----------------------|---------------------------|

| ES-TRNG | $297\mathrm{GE}$ | $0.135803\mathrm{ns}$ | $2.2\mathrm{Mbit/s}$      |

#### **Table 1:** ES-TRNG in a 65 nm low-power CMOS technology @ 100 MHz system clock.

#### 3.3 Permutations vs. Block Ciphers vs. Stream Ciphers

Having concluded negatively on the suitability of TRNG instances to generate random values for (parallel, higher-order) hardware masking, we now compare a number of potentially cost-efficient cryptographic building blocks based on their throughput-area ratio to be used in PRNG constructions. We rely on prior efficiency comparisons to pre-select such primitives. In more detail, the authors of [AZ21] compared the Round 2 candidates of the NIST lightweight cryptography standardization process [oSN17] based on their ASIC implementation figures. Several different metrics are evaluated, including throughput and throughput-area ratio. The lightweight primitive Subterranean 2.0, introduced in [DMMR20], offers by far the best throughput-area ratio, while the cross-platform permutation Gimli, proposed in [BKL<sup>+</sup>17], offers one of the best throughput figures. Both of these primitives are included in our further investigation. According to the comparison of low-latency ciphers given in [LMMR21], the 5-round version of the ultra low-latency cipher SPEEDY, called SPEEDY-5-192 requires a smaller area per output bit and can be clocked at a higher frequency than any other low-latency primitive when implemented fully-unrolled in hardware. Finally, the comparison of all 8 stream ciphers in the hardware profile of the eSTREAM competition that reached the third phase are compared for their cost and efficiency in [GB08]. The stream cipher Trivium [Can06, CP08] offers by far the best throughput-area ratio among all its competitors, hence, we include it in our preliminary investigation as well. Other related works reached similar conclusions [GLB+06, BKSQ07, GSB07, Rog07, HCK+08, LLL20]

#### 3.3.1 Full-Security Versions

To summarize, in our initial comparison we have selected two of the most cost-efficient building blocks from the NIST lightweight cryptography competition, the supposedly most cost-efficient low-latency cipher and the supposedly most cost-efficient hardware stream cipher from the eSTREAM competition. The corresponding synthesis results are given in Table 2 for 4 different ASIC standard cell libraries, 2 commercial ones and 2 open-source ones. The synthesis tool used is *Synopsys Design Compiler Version O-2018.06-SP4*. Our Subterranean 2.0, Gimli and SPEEDY hardware implementation results are based on publicly available source code that can be found here:

- Subterranean 2.0: https://github.com/pmassolino/hw-subterranean

- Gimli: https://gimli.cr.yp.to/impl.html

- SPEEDY: https://github.com/Chair-for-Security-Engineering/SPEEDY

The complete set of individual delay, area, power consumption and throughput figures, in addition to combined metrics such as energy consumption per bit and power-area-time product, are listed for each candidate in Appendix A. It is important to note that we compare the raw primitives in this initial comparison and do not consider any framework that is needed to turn them into usable PRNGs (typically required for the block-oriented primitives, but not for stream ciphers). For the block ciphers and permutations, two different versions are considered: (i) a fully-unrolled single-cycle implementation from combinatorial logic only and (ii) a fully-unrolled round-pipelined implementation ( $\checkmark$ ). For Gimli and SPEEDY, 24 and 5 cipher rounds are unrolled respectively. Both versions (i)

and (ii) produce one block of output per clock cycle. Yet, the pipelined versions obviously require a number of cycles equal to the number of rounds before the first usable output is produced. We also acknowledge that efficiently initializing such large pipelines, for example  $24 \cdot 384 = 9216$  bits in case of Gimli, while keeping the initial seed small, might become difficult. For Trivium the situation is different, as common stream ciphers are not based on iterative round functions. Instead, they are typically constructed from state update functions that produce a single output bit or word per step while updating the state register. As discussed in Section 2, these update functions can be unrolled in a similar manner as the round functions of a block cipher or permutation, with the additional advantage that state update functions can be sparse and chosen in such a way that a certain degree of unrolling leads to no increase of the gate depth or critical path. In fact, the structure of Trivium allows it to be implemented in a way that neither the depth nor the delay of the hardware circuit are increased for 64 bits of unrolling or below, making Trivium X64 the most cost efficient primitive in Table 2. Trivium\_X48 and Trivium\_X64 outperform Trivium\_X32, Trivium\_72 and any larger (> 72) or lower (< 32) unrolling level. We evaluated Trivium for many degrees of unrolling (arbitrary degrees are possible, see also Section 5), but none of them offered a better throughput-area ratio than Trivium X64 in (bits/s)/GE. Of course, when integrated into a larger chip design where other components demand a lower operating frequency, larger unrolling factors are still more attractive in order to fully exhaust the critical path budget and generate as many bits per cycle as possible. Since the degree of unrolling can be chosen arbitrarily, the number of output bits produced per cycle is adjustable with single-bit granularity, which also provides a conveniently high flexibility compared to permutations and block ciphers.

Subterranean 2.0 is a hybrid primitive that is hard to put in a category. It uses elements from permutation-based cryptography and resembles a sponge-like construction that behaves like a stream cipher when squeezed, producing 32-bit words per step. Its round/update function can be unrolled to provide even more bits per cycle, but unlike Trivium, unrolling will not improve its TPA in (bits/s)/GE. Instead, the standard variant producing 32 bits per cycle is the most cost-efficient one in this metric and makes it the second most cost-efficient primitive in two of the four considered standard cell libraries in Table 2. Yet, its throughput-area ratio is 4 times lower compared to Trivium\_X64, mostly because it occupies a larger area while only producing half the number of bits per cycle (c.f. Table 7). Its power consumption, however, is up to 30 % lower than unrolled Trivium's (c.f. Table 8). Round-pipelined Gimli performs similarly well and places second in the other two cell libraries. Yet, it comes at a much higher default cost ( $\approx$  70-90 kGE compared to Trivium\_X64's 4-5 kGE). Round-pipelined SPEEDY is roughly half as cost-efficient as Gimli and Subterranean 2.0 here.

Note that the throughput-area ratio of Trivium\_X64 is 77.51 (Mbit/s)/GE in Nan-Gate 45 nm library, more than 13% larger than the 68.14 (Mbit/s)/GE achieved by the PRNG based on evolutionary programming presented in [PYR<sup>+</sup>16] using the same library. We believe it is a strong result that Trivium, a stream cipher with proven cryptographic strength that has been analyzed for almost 20 years, leads to more cost-efficient implementations in hardware than dedicated PRNGs for mask generation that only achieve sufficient statistical properties to pass common test suites without cryptographic guarantees.

#### 3.3.2 Reduced-Security Versions

Yet, as explained in detail in Section 1, full 80-bit or 128-bit security may not always be needed for PRNGs in masking contexts, as adversaries may at most obtain a noisy version of the PRNG's output through side-channel observations. Performing cryptanalytic attacks or solving complex systems of equations based on partially erroneous data is known to be a hard problem. The security of modern lattice-based post-quantum cryptography for instance depends on the hardness of computational problems such as Learning With

|                   |      |            | Throughput/Area [(Mbit/s)/GE] |                    |                 |                 |  |

|-------------------|------|------------|-------------------------------|--------------------|-----------------|-----------------|--|

|                   |      |            | Commercia                     | al Foundry         | NanGate OCI     |                 |  |

| Primitive         | pip. | bits/cycle | $90\mathrm{nm}\mathrm{LP}$    | $65\mathrm{nm}$ LP | $45\mathrm{nm}$ | $15\mathrm{nm}$ |  |

| Subterranean2     |      | 32         | 14.272                        | 17.848             | 15.610          | 156.644         |  |

| Subterranean2_X2  |      | 64         | 9.430                         | 11.418             | 10.461          | 92.776          |  |

| Subterranean2_X4  |      | 128        | 5.422                         | 6.786              | 6.987           | 60.899          |  |

| Subterranean2_X8  |      | 256        | 2.910                         | 3.309              | 3.859           | 32.578          |  |

|                   |      | 384        | 1.254                         | 1.540              | 1.739           | 16.351          |  |

| Gimli (24 rounds) | 1    | 384        | 13.518                        | 15.875             | 16.561          | 162.556         |  |

| ODEEDV F 100      |      | 192        | 1.354                         | 1.637              | 2.159           | 18.442          |  |

| SPEEDY-5-192      | 1    | 192        | 7.446                         | 10.146             | 8.857           | 75.990          |  |

| Trivium           |      | 1          | 2.356                         | 4.072              | 2.189           | 22.232          |  |

| Trivium_X32       |      | 32         | 51.292                        | 46.261             | 46.827          | 412.244         |  |

| Trivium_X48       |      | 48         | 48.623                        | 63.186             | 57.639          | 607.553         |  |

| Trivium_X64       |      | 64         | 58.899                        | 73.785             | 77.514          | 752.875         |  |

| Trivium_X72       |      | 72         | 42.484                        | 59.694             | 61.534          | 530.410         |  |

**Table 2:** Comparison of the throughput-area ratio of unrolled building blocks, including the stream cipher Trivium, the lightweight primitive Subterranean 2.0, the cross-platform permutation Gimli and the ultra low-latency cipher SPEEDY. Values are obtained when optimizing for maximum frequency (constrained clock period).

Errors (LWE), which requires solving a system of noisy linear equations. Hence, lower security levels in the black-box model can lead to much higher security levels against adversaries with access to noisy data only [DFH<sup>+</sup>16]. For this reason our concrete setting might tolerate lower security levels if the cost-efficiency can be improved significantly. In this context, the advantage of block ciphers and permutations over stream ciphers is that the number of rounds can be adapted in order to flexibly adjust the security-vs-performance tradeoff. In fact, it is possible for most modern block ciphers and permutations to remove multiple rounds and still maintain a security level beyond enumeration power. For stream ciphers, no such well-understood mechanism exists (shortening the initialization phase reduces security but brings no gains in hardware performance during keystream generation). Luckily, in case of Trivium, the reduced security variant Bivium has been introduced as a study object for cryptanalytic reasoning. Hence, we also compare Bivium to round-reduced versions of the previously analyzed building blocks Gimli and SPEEDY in Table 3. The smallest round-reduced versions (8-round Gimli and 2-round SPEEDY) chosen here can both be practically broken in the black-box setting (distinguishers with complexities below  $2^{40}$  exist), but attacks are still expected to require a computational effort that becomes prohibitive when only partial information on inputs and outputs is available. Bivium X64 clearly outperforms the reduced security primitives in TPA. Here, round-pipelined 8round Gimli performs best among the remaining primitives, with approximately half the throughput-area ratio compared to Bivium\_X64, while also consuming a 9 times larger area and 10 times more power on average (c.f. Table 7 and Table 8). Reduced-round SPEEDY achieves less than a quarter of the cost efficiency of Bivium\_X64. The results in Table 2 and Table 3 show that Trivium and Bivium are the best performing candidates in TPA for full and reduced security.

## 3.4 Other Stream Ciphers

The observation that stream ciphers can outperform block-based encryption algorithms in throughput-area ratio is not new. Stream ciphers are known to require a smaller area

|                   |      |            | Throughput/Area [(Mbit/s)/GE] |                    |                 |                 |  |

|-------------------|------|------------|-------------------------------|--------------------|-----------------|-----------------|--|

|                   |      |            | Commercial Foundry            |                    | NanGa           | te OCL          |  |

| Primitive         | pip. | bits/cycle | $90\mathrm{nm}\mathrm{LP}$    | $65\mathrm{nm}$ LP | $45\mathrm{nm}$ | $15\mathrm{nm}$ |  |

| (imli (9 mounda)  |      | 384        | 8.619                         | 10.544             | 12.839          | 108.180         |  |

| Gimli (8 rounds)  | 1    | 384        | 42.754                        | 44.256             | 49.251          | 480.270         |  |

| Gimli (16 rounds) |      | 384        | 2.484                         | 2.996              | 4.273           | 36.684          |  |

| Gimii (16 rounds) | 1    | 384        | 20.603                        | 25.763             | 23.827          | 243.939         |  |

| SPEEDY-2-192      |      | 192        | 10.429                        | 12.539             | 15.224          | 134.877         |  |

| SPEEDI-2-192      | 1    | 192        | 19.734                        | 25.811             | 24.427          | 242.620         |  |

| SPEEDY-3-192      |      | 192        | 4.155                         | 4.918              | 6.359           | 55.208          |  |

| SPEEDI-S-192      | 1    | 192        | 12.513                        | 16.790             | 15.249          | 134.630         |  |

| SPEEDY-4-192      |      | 192        | 2.183                         | 2.751              | 3.425           | 29.738          |  |

| SPEED1-4-192      | 1    | 192        | 9.297                         | 12.971             | 11.013          | 96.851          |  |

| Bivium            |      | 1          | 3.624                         | 5.364              | 3.544           | 34.050          |  |

| Bivium_X32        |      | 32         | 70.893                        | 77.847             | 71.559          | 690.677         |  |

| Bivium_X48        |      | 48         | 75.572                        | 96.861             | 107.462         | 969.275         |  |

| Bivium_X64        |      | 64         | 89.620                        | 107.543            | 109.730         | 1212.312        |  |

| Bivium_X72        |      | 72         | 66.909                        | 90.785             | 81.547          | 809.863         |  |

**Table 3:** Comparison of the throughput-area ratio of the reduced-security versions of the primitives from Table 2. Values are obtained when optimizing for maximum frequency (constrained clock period).

footprint in hardware (on average) compared to block ciphers with similar security levels and have therefore been of primary interest for resource-constrained devices such as smart cards, sensor networks or Radio-Frequency Identification (RFID) tags [BKSQ07]. Since Trivium delivered very promising results in the preliminary analysis, we now investigate whether other stream ciphers can provide similarly impressive performance for randomness generation.

The eSTREAM competition was held from 2004 to 2008 with the goal to identify and collect secure and compact stream cipher proposals suitable for widespread adoption; separately for a hardware and software profile [oEiCE04]. During this time, researchers have compared many of the proposed stream ciphers to each other and also to older standards such as A5/1 [BGW98], RC4 [Sch96] or E0 [E02], resulting in a number of publications containing performance rankings of multiple candidates [GB08, GLB<sup>+</sup>06, BKSQ07, GSB07, Rog07, HCK<sup>+</sup>08]. They all have in common that Trivium is identified as the number one candidate with respect to throughput-area ratio, although among different sets of primitives, most oftenly followed by Grain v1 (either the 80- or 128-bit key variant). Also for the maximum throughput, Trivium places first in all works that have implemented its 64-bit unrolled variant [GB08, GLB<sup>+</sup>06, GSB07, Rog07, HCK<sup>+</sup>08]. The top rank for minimum area is mostly split between Trivium, Grain v1 [HJM07, HJMM06], MICKEY 2.0 [BD08] when considering only eSTREAM candidates - with the insecure A5/1 algorithm (broken in practical time since the year 2000 [BD00]) being consistently smaller. Two further comparisons have been published several years after the eSTREAM competition ended, namely [KSPS13] in 2013 and [LLL20] in 2020, which also include more recent stream cipher proposals. While the work by Kitsos et al. favors MICKEY 2.0 over Trivium or Grain v1 for maximizing the throughput-area ratio, this is mostly due to the fact that only the basic non-unrolled versions of the latter have been implemented [KSPS13]. This is also criticized by Li et al. [LLL20], who provide implementation figures including unrolled Trivium and Grain v1 and report an advantage of Trivium over MICKEY 2.0 in TPA by more than an order of magnitude. In total, all listed publications collectively

include the following set of stream ciphers (or variants of them) implemented in hardware: A5/1 [BGW98], RC4 [Sch96], E0 [E02], SNOW3G [SNO], Phelix [WSLM05], Lex [Bir08], Achterbahn [GGK05], MOSQUITO [DK05], SFINKS [BLM<sup>+</sup>05], VEST [OGL05], ZK-Crypt [GGV05], Trivium [CP08], Grain v1 [HJM07, HJMM06], MICKEY 2.0 [BD08], DECIM [BBC<sup>+</sup>08], Edon80 [GMK08], F-FCSR [ABL08], Moustique [DK08], Pomaranch [JHK08], Salsa20 [Ber08], ZUC [ZUC], Plantlet [MAM16] and Lizard [HKM17]. Among all these primitives, the candidates consistently performing best in maximum throughput, minimum area and maximum throughput-area ratio (without being broken in practical time complexity yet) are Trivium, Grain v1 (80- and 128-bit variant) and MICKEY 2.0 (80- and 128-bit variant). These are, not surprisingly, also the three candidates that have been selected for the hardware portfolio of the eSTREAM competition. Hence, we decided to select these three primitives for a closer look at stream cipher performances for mask generation. While, to the best of our knowledge, no cryptanalytic attacks against full Trivium or full MICKEY 2.0 exist, key recovery attacks against both Grain v1 variants (80- and 128-bit key) with complexities below exhaustive key search are known [TIM<sup>+</sup>18, BCM23]. However, the complexities remain significant enough to not disregard these primitives for our purposes, as the performance of the attacks is still prohibitive for most computationally bounded adversaries even in the noise-free setting (approximately  $2^{75}$  and  $2^{112}$  respectively). Since we take a look at 80- and 128-bit variants of both Grain and MICKEY, we also consider a 128-bit secure version of Trivium for this exercise, which is called Kreyvium and has been first proposed at FSE 2016 for efficient homomorphic encryption  $[CCF^+16]$ . Unlike the 128-bit versions of Grain and MICKEY, Kreyvium is not a real re-design of its successor based on larger parameters, but mostly relies on keeping original Trivium intact and extending it by two additional registers holding the 128-bit key and 128-bit IV, which are never updated beyond a rotation of the bits. This change, while promising for the purposes intended by the authors, is not exactly optimal to improve the throughput-area ratio.

The full comparison is shown in Table 4; individual delay, area, power consumption and throughput figures in addition to combined metrics (energy consumption per bit, power-area-time product) can be found in Appendix A. As already pointed out in previous stream cipher comparisons, the optimal level of unrolling to maximize the throughput-area ratio differs between the candidates. For Grain v1 with 80-bit key and 128-bit key it is 16 and 32 respectively, for Trivium and Kreyvium it is 64 (because the core design is identical) and for MICKEY 2.0 with 80-bit key and 128-bit key it is actually 1. The MICKEY design is not based on the principle that recently updated state bits are not used in the next X update steps. Hence, unrolling this stream cipher will not lead to any improved results in the (bits/s)/GE metric (doubling the output bits per cycle will also increase both delay and area of the combinational logic approximately by factor 2, resulting in a lower TPA overall). To still have a common denominator between all designs for comparison purposes, we made sure to evaluate a 32-bit unrolled version of each of them. While the small size and power consumption of Grain v1 is attractive (c.f., Table 7; similar to Bivium), its update function has a larger gate depth than Trivium's and the number of consecutive update functions based on independent bits is too small to reach the throughput-area of Trivium. In fact, Subterranean 2.0 and round-pipelined Gimli achieve better TPA than both Grain v1 variants (c.f., Table 2). MICKEY 2.0 is only competitive when no unrolling is considered, making it a poor choice for our purposes. Additionally, it has received the least amount of cryptanalysis among the three eSTREAM candidates considered here and it has been pointed out that its data-dependent irregular clocking may lead to simple, timing-based side-channel attacks [GBC<sup>+</sup>08], which is undesirable in our setting. Finally, we extrapolated the critical path values given in Appendix A Table 6 to estimate how many bits per cycle can at most be generated by each of the stream ciphers (i.e., the maximum level of unrolling) in 65 nm ASIC technology at 100MHz operating frequency. The results show that Bivium, Trivium and Kreyvium may generate over 3000 bits per cycle, while the Grain v1 variants achieve 400 (for the 80-bit key) and 1000 bits (for the 128-bit key) respectively. Both MICKEY 2.0 versions may generate at most 50 bits per cycle. Again, we conclude that Trivium and its variants are the most promising cryptographic algorithms for maximizing the throughput-area ratio and thus great candidates for cost efficient and secure randomness generation in hardware.

**Table 4:** Comparison of the throughput-area ratio of unrolled stream ciphers. Values are obtained when optimizing for maximum frequency (constrained clock period).

|                                      |            |            | Throughput/Area [(Mbit/s)/GE] |                    |                 |                 |

|--------------------------------------|------------|------------|-------------------------------|--------------------|-----------------|-----------------|

|                                      |            |            | Commerci                      | al Foundry         | NanGa           | ate OCL         |

| Primitive                            | key length | bits/cycle | $90\mathrm{nm}\mathrm{LP}$    | $65\mathrm{nm}$ LP | $45\mathrm{nm}$ | $15\mathrm{nm}$ |

| GrainV1_80                           |            | 1          | 1.464                         | 2.020              | 1.580           | 14.825          |

| GrainV1_80_X8                        | 80         | 8          | 6.391                         | 7.849              | 7.287           | 69.252          |

| $GrainV1_80_X16^*$                   | 80         | 16         | 8.274                         | 10.861             | 9.031           | 86.915          |

| GrainV1_80_X32                       |            | 32         | 5.817                         | 7.023              | 7.158           | 61.417          |

| GrainV1_128                          |            | 1          | 1.086                         | 1.484              | 1.093           | 9.841           |

| GrainV1_128_X16                      | 128        | 16         | 8.522                         | 11.465             | 9.751           | 91.195          |

| $GrainV1_{128}X32^*$                 | 120        | 32         | 12.410                        | 18.556             | 13.996          | 130.803         |

| GrainV1_128_X48                      |            | 48         | 8.907                         | 11.978             | 11.195          | 94.795          |

| MICKEY2_80*                          |            | 1          | 1.224                         | 1.807              | 1.391           | 11.291          |

| MICKEY2_80_X2                        | 80         | 2          | 0.967                         | 1.440              | 1.108           | 9.191           |

| MICKEY2_80_X4                        | 80         | 4          | 0.621                         | 0.835              | 0.763           | 6.627           |

| MICKEY2_80_X32                       |            | 32         | 0.056                         | 0.077              | 0.068           | 0.642           |

| $MICKEY2_{128}^*$                    |            | 1          | 0.778                         | 0.967              | 0.885           | 6.247           |

| MICKEY2_128_X2                       | 128        | 2          | 0.575                         | 0.817              | 0.652           | 5.602           |

| MICKEY2_128_X4                       | 120        | 4          | 0.360                         | 0.496              | 0.443           | 3.603           |

| MICKEY2_128_X32                      |            | 32         | 0.033                         | 0.046              | 0.039           | 0.359           |

| Trivium                              |            | 1          | 2.356                         | 4.072              | 2.189           | 22.232          |

| Trivium_X32                          |            | 32         | 51.292                        | 46.261             | 46.827          | 412.244         |

| Trivium_X48                          | 80         | 48         | 48.623                        | 63.186             | 57.639          | 607.553         |

| $\texttt{Trivium}_{X64^*}$           |            | 64         | 58.899                        | 73.785             | 77.514          | 752.875         |

| Trivium_X72                          |            | 72         | 42.484                        | 59.694             | 61.534          | 530.410         |

| Kreyvium                             |            | 1          | 0.982                         | 1.240              | 1.027           | 9.218           |

| Kreyvium_X32                         |            | 32         | 21.554                        | 27.449             | 23.696          | 233.767         |

| Kreyvium_X48                         | 128        | 48         | 29.554                        | 36.597             | 33.600          | 325.753         |

| $\texttt{Kreyvium}_{\texttt{X64}^*}$ |            | 64         | 37.142                        | 45.264             | 37.719          | 388.195         |

| Kreyvium_X72                         |            | 72         | 27.773                        | 38.244             | 32.134          | 291.893         |

\* Optimal level of unrolling to maximize Throughput/Area ratio.

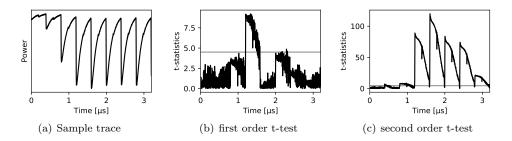

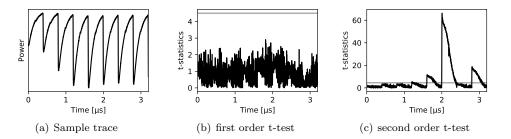

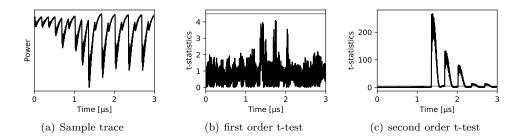

# 3.5 LFSRs